|

В.А. Авдеев, В.Ф. Гузик

Компьютеры: шины, контроллеры, периферийные устройства

Учебное пособие. Таганрог: ТРТУ, 2001. - 536 с.

2. Системные интерфейсы

2.1. Системный интерфейс MULTIBUS

Системный

интерфейс Multibus является магистральным (машинным и

многопроцессорным) интерфейсом с квитированием. Интерфейсы с квитированием

иногда называют асинхронными интерфейсами. Интерфейс Multibus удовлетворяет требованиям стандарта,

принятым Институтом по электронике и электротехнике (IEEE) и является аналогом интерфейса IEEE 796. Различают интерфейс Multibus–1, проложивший путь к многошинному подходу построения

интерфейсов, и интерфейс Multibus–2,

совершенствующий первый и расширяющий диапазон его применения (например,

использования 32-разрядных микропроцессоров, реализации монопольного режима

передачи данных, применения параллельных и последовательных системных шин и так

далее). В предлагаемой главе основное внимание уделяется интерфейсу Multibus–1 (в дальнейшем просто Multibus). Аналогом интерфейса Multibus является отечественный интерфейс И41.

Интерфейс Multibus может быть использован для

построения вычислительных систем на базе 32–разрядных (64–разрядных) микропроцессоров.

Для простого

варианта ПК задатчик (процессор) выполняет выбор ячейки ОП с помощью 20–разрядного

адреса, устанавливаемого на линиях (односторонней шины адреса)  – – . С

целью доступа к регистрам ПУ используется 10–разрядный адрес . С

целью доступа к регистрам ПУ используется 10–разрядный адрес  – – ,

причем разряд А0 является младшим. Передача данных осуществляется по

двунаправленной шине данных ,

причем разряд А0 является младшим. Передача данных осуществляется по

двунаправленной шине данных  – – (бит D0 – младший). Логическая 1 на шинах адреса и данных

представляется низким уровнем (Н), а логический 0 – высоким уровнем (В) сигнала

(инверсная логика). Чтобы подчеркнуть этот факт, разряды адреса и данных

изображаются на схемах с чертой над символом, например, (бит D0 – младший). Логическая 1 на шинах адреса и данных

представляется низким уровнем (Н), а логический 0 – высоким уровнем (В) сигнала

(инверсная логика). Чтобы подчеркнуть этот факт, разряды адреса и данных

изображаются на схемах с чертой над символом, например,  – – и и  – – . Следующий пример показывает

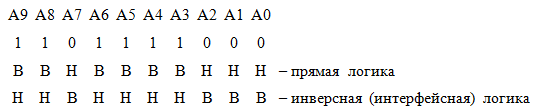

представление уровней адреса 378h (h – знак

16-ричной записи) регистра адаптера ПУ на шине адреса интерфейса. . Следующий пример показывает

представление уровней адреса 378h (h – знак

16-ричной записи) регистра адаптера ПУ на шине адреса интерфейса.

Интерфейс

обеспечивает выполнение следующих процедур: арбитраж, прерывание и пересылку

данных. Кроме того, обмен данными между задатчиком и исполнителем через

интерфейс может быть выполнен в режимах безусловного и условного (с опросом

флага готовности) программного обмена по инициативе процессора , обмена в

режиме прерывания по инициативе ПУ процессора и обмена в режиме прямого доступа

к памяти (ПДП), при котором аппаратно реализуется передача данных между ОП и ВЗУ.

Процедура

прерывания имеет два варианта реализации : прерывание с интерфейсным вектором и

прерывание с внеинтерфейсным вектором. В первом случае адрес вектора прерывания

передается по шине данных интерфейса от исполнителя к задатчику, а во втором

случае – не передается. В ПК наиболее употребительным является внеинтерфейсное

прерывание, при котором в контроллер прерывания задатчика поступают запросы

прерывания по интерфейсным линиям   – –   . Сигнал . Сигнал   имеет наивысший приоритет и его

формирует системный таймер (часы) ПК. Запрос имеет наивысший приоритет и его

формирует системный таймер (часы) ПК. Запрос   вырабатывает клавиатура. Прерывание

заключается в переходе на программу обработки прерывания по 4–байтному коду

(вектору прерывания), хранящемуся в памяти и определяющему программу

обслуживания (драйвер) ПУ, требующего прерывание. Адрес вектора прерывания

(адрес ячейки памяти) используется для нахождения этого вектора. Различают

немаскируемые внутренние и внешние прерывания (например, при делении на 0,

прерывание от процессора) и внешние (маскируемые) прерывания от адаптеров ПУ. вырабатывает клавиатура. Прерывание

заключается в переходе на программу обработки прерывания по 4–байтному коду

(вектору прерывания), хранящемуся в памяти и определяющему программу

обслуживания (драйвер) ПУ, требующего прерывание. Адрес вектора прерывания

(адрес ячейки памяти) используется для нахождения этого вектора. Различают

немаскируемые внутренние и внешние прерывания (например, при делении на 0,

прерывание от процессора) и внешние (маскируемые) прерывания от адаптеров ПУ.

В интерфейсе

реализуются следующие пересылки данных: запись в порт (ячейку памяти) и чтение

из порта (ячейки памяти). Для реализации этих операций используются

интерфейсные сигналы: чтение порта ( ), чтение памяти ( ), чтение памяти ( ), запись в порт ( ), запись в порт ( ),

запись в память ( ),

запись в память ( ), которые формируются задатчиком

З ), которые формируются задатчиком

З . Обмен осуществляется в режиме

квитирования с формированием исполнителем ответного сигнала . Обмен осуществляется в режиме

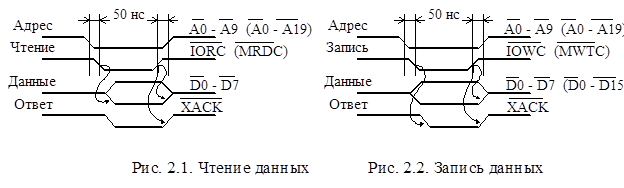

квитирования с формированием исполнителем ответного сигнала  . Временные диаграммы чтения данных из

порта (памяти) и записи данных в порт (память) представлены соответственно на рис.

2.1и 2.2. . Временные диаграммы чтения данных из

порта (памяти) и записи данных в порт (память) представлены соответственно на рис.

2.1и 2.2.

Из временной

диаграммы видно, что сигнал  ( ( ) должен быть установлен не менее чем за 50

нс после выдачи адреса. Этот период времени необходим для компенсации

переходных процессов, связанных с декодированием адреса исполнителем. Кроме

того, после снятия сигнала ) должен быть установлен не менее чем за 50

нс после выдачи адреса. Этот период времени необходим для компенсации

переходных процессов, связанных с декодированием адреса исполнителем. Кроме

того, после снятия сигнала  ( ( ) адрес должен оставаться на линиях шины

минимум 50 нс. Ответный сигнал ) адрес должен оставаться на линиях шины

минимум 50 нс. Ответный сигнал  может совпадать по

времени с моментом выдачи данных или следовать за ним. Сброс может совпадать по

времени с моментом выдачи данных или следовать за ним. Сброс  выполняется после снятия выполняется после снятия  ( ( ). Сигнал ). Сигнал

удерживается максимум 65 нс после снятия

сигнала удерживается максимум 65 нс после снятия

сигнала  ( ( ) или ) или  ( ( ). При

записи адрес и данные должны быть установлены как минимум за 50 нс до появления

сигнала ). При

записи адрес и данные должны быть установлены как минимум за 50 нс до появления

сигнала  ( ( ) и

сняты спустя не менее чем через 50 нс после сброса ) и

сняты спустя не менее чем через 50 нс после сброса  ( ( ). Эта задержка связана, во–первых, с

необходимостью декодирования адреса и, во–вторых, с целью возможности записи

данных как по переднему, так и по заднему фронту сигнала ). Эта задержка связана, во–первых, с

необходимостью декодирования адреса и, во–вторых, с целью возможности записи

данных как по переднему, так и по заднему фронту сигнала  ( ( ). На

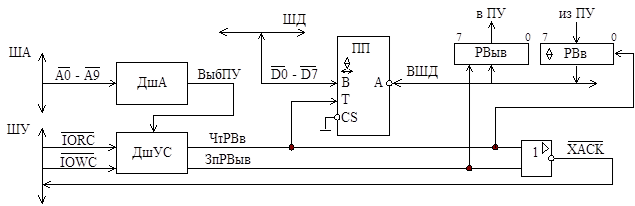

рис. 2.3 показана структурная схема подключения к интерфейсу следующих портов:

регистра ввода (РВв) и регистра вывода (РВыв). ). На

рис. 2.3 показана структурная схема подключения к интерфейсу следующих портов:

регистра ввода (РВв) и регистра вывода (РВыв).

Рис. 2.3. Структурная схема

подключения РВв и РВыв к интерфейсу

Термины Ввод

или Вывод следует всегда рассматривать относительно П, т.е. П выводит байт

данных и записывает в порт РВыв ПУ или П читает содержимое порта РВв ПУ и

вводит в собственные регистры. Под портом понимается адресуемый триггер,

регистр или схема. Схема (см. рис. 2.3.) содержит шину адреса (ША), шину

управления (ШУ), шину данных (ШД) интерфейса, дешифратор адреса (ДшА), дешифратор

управляющих сигналов (ДшУС), приемопередатчик (ПП), 8–разрядные регистры РВв и РВыв

и передатчик, формирующий  . Рассмотрим работу

схемы в режиме вывода данных (записи в РВыв) в соответствии с временной

диаграммой (см. рис. 2.2). П устанавливает адрес . Рассмотрим работу

схемы в режиме вывода данных (записи в РВыв) в соответствии с временной

диаграммой (см. рис. 2.2). П устанавливает адрес  – – на ША и данные на ША и данные  – – на ШД интерфейса. Адрес и данные

поступают на все ПУ, подключенные к интерфейсу, но только одно ПУ с помощью ДшА

декодирует собственный адрес, например 3С0h. В этом случае на выходе ДшА формируется сигнал ВыбПУ, разрешающий

работу ДшУС. Данные проходят через ПП, открытый для передачи от В к А (от ШД к

внутренней шины данных (ВШД)). ПП выполняет двустороннюю передачу данных в

зависимости от сигнала на входе Т. Если Т=1, то данные передаются с ВШД на ШД интерфейса.

Если Т=0, то наоборот (ШД®ВШД).

Так как в этот момент времени сигнал ЧтРВыв=0 (пассивный уровень), то данные

проходят через ПП и поступают на входы РВыв. Через 50 нс после декодирования

адреса (формирования сигнала ВыбПУ) П устанавливает сигнал записи на ШД интерфейса. Адрес и данные

поступают на все ПУ, подключенные к интерфейсу, но только одно ПУ с помощью ДшА

декодирует собственный адрес, например 3С0h. В этом случае на выходе ДшА формируется сигнал ВыбПУ, разрешающий

работу ДшУС. Данные проходят через ПП, открытый для передачи от В к А (от ШД к

внутренней шины данных (ВШД)). ПП выполняет двустороннюю передачу данных в

зависимости от сигнала на входе Т. Если Т=1, то данные передаются с ВШД на ШД интерфейса.

Если Т=0, то наоборот (ШД®ВШД).

Так как в этот момент времени сигнал ЧтРВыв=0 (пассивный уровень), то данные

проходят через ПП и поступают на входы РВыв. Через 50 нс после декодирования

адреса (формирования сигнала ВыбПУ) П устанавливает сигнал записи  , по которому ДшУС вырабатывает сигнал ЗпРВыв=1

(активный уровень), записывающий данные с ВШД в РВыв и формирующий сигнал

квитирования , по которому ДшУС вырабатывает сигнал ЗпРВыв=1

(активный уровень), записывающий данные с ВШД в РВыв и формирующий сигнал

квитирования  , сообщающий П о завершении операции.

Если сигнал , сообщающий П о завершении операции.

Если сигнал  не поступает в П, то считается, что

произошла ошибка на интерфейсе. В качестве ПП может быть использована микросхема

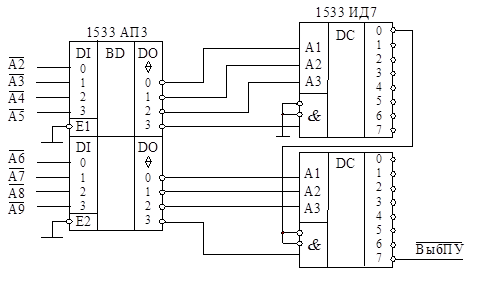

580 ВА87, а ДшА мажет быть реализован на двух микросхемах 1533 ИД7. Рассмотрим

более сложный пример. Пусть адаптер содержит четыре адресуемых регистра: не поступает в П, то считается, что

произошла ошибка на интерфейсе. В качестве ПП может быть использована микросхема

580 ВА87, а ДшА мажет быть реализован на двух микросхемах 1533 ИД7. Рассмотрим

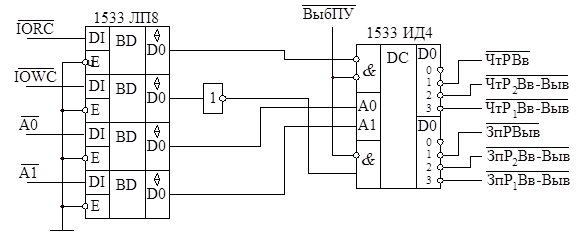

более сложный пример. Пусть адаптер содержит четыре адресуемых регистра:  –Выв (адрес 3С0h), –Выв (адрес 3С0h),  –Выв (адрес 3С1h), РВв (адрес 3С2h) и РВыв (адрес 3С2h). Для этого случая принципиальная

схема ДшА показана на рис. 2.4, а ДшУС – на рис. 2.5. –Выв (адрес 3С1h), РВв (адрес 3С2h) и РВыв (адрес 3С2h). Для этого случая принципиальная

схема ДшА показана на рис. 2.4, а ДшУС – на рис. 2.5.

Рис. 2.4. Принципиальная схема ДшА

Рис. 2.5. Принципиальная схема ДшУС

При построении принципиальных схем учитывались следующие

обязательства : для согласования интерфейса со схемами ТТЛ необходимо применять

специальные буферные схемы (1533 АП3 и 1533 ЛП8 и т.д.), логическая 1 на шине

адреса представлена низким уровнем, а логический 0 – высоким уровнем и регистры

–Выв и –Выв и  –Выв доступны

по записи и чтению со стороны П. При обращении к любому порту необходимо

сформировать сигнал квитирования –Выв доступны

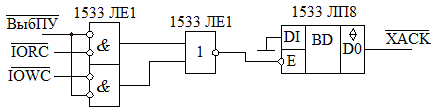

по записи и чтению со стороны П. При обращении к любому порту необходимо

сформировать сигнал квитирования  (рис. 2.6). (рис. 2.6).

Рис. 2.6. Принципиальная схема формирования

Похожие материалы:

Системный анализ

Системные подходы к управлению инновационной деятельностью компаний. Выводы - Тычинский, 2006

Системная шина EISA

Системообразующее значение и экономическое содержание инновационной деятельности компаний

Системы и принципы ведения бухгалтерского учета (Федосова Т.В.)

Системы и принципы ведения бухгалтерского учета

|