|

В.А. Авдеев, В.Ф. Гузик

Компьютеры: шины, контроллеры, периферийные устройства

Учебное пособие. Таганрог: ТРТУ, 2001. - 536 с.

2. Системные интерфейсы

2.2. Шина расширения ISA

Системная

шина IBM PC/XT предназначена для работы с 8–разрядными

микропроцессорами (МП), поэтому содержит 8 линий шины данных (D0–D7). Кроме того, системная шина включает 20–разрядную шину

адреса (А0–А19). Шина управления имеет линии, связанные с организацией ПДП,

прерывания, доступа к портам (памяти) и т.д. Для подключения адаптеров (плат

расширения) используются 62–контактные разъемы (слоты). Кроме того,

синхронизация П и системной шины осуществляется от одного генератора тактовых

сигналов с частотой 4,77 МГц.

Системная

шина ISA (промышленная стандартная

архитектура) – это 16–разрядная шина расширения, допускающая подключение как 8–разрядных,

так и 16–разрядных адаптерных плат. Системная шина дополнительно содержит 36–контактный

разъем для расширения функциональных возможностей (увеличение линий данных,

адреса, прямого доступа и прерываний). Синхронизация работы П и шины ISA выполняется асинхронно, то есть

разными тактовыми частотами сигналов. Тактовая частота работы шины ISA равна 8 МГц.

Шина ISA отличается

от интерфейса Multibus тем, что большое число сигналов имеет активный высокий

уровень (поэтому используются обозначения А0–А23 и D0–D15 без черты над символами)

и отсутствует сигнал квитирования.

Шина ISA полностью

совместима с системной шиной IBM PC/XT, то есть все платы адаптеров ПУ IBM PC/XT

могут быть подключены к шине ISA. Рассмотрим основные интерфейсные сигналы,

необходимые для подключения адаптерных плат к шине ISA. Сигналы на линиях шины

адреса А0–А23 устанавливаются задатчиком (имеют три состояния и активный

высокий уровень). Для доступа к портам используются биты А0–А9 (в пределах

материнской платы) или А0–А15. Двунаправленные линии D0–D15 образуют шину

данных. Каждая линия Di имеет три состояния: высокий (активный) уровень, низкий (пассивный)

уровень и выключено. Сигнал разрешения адреса (AEN) устанавливается

контроллером ПДП. Низкий уровень этого сигнала указывает на обычный ввод–вывод

(обращение к портам), а высокий уровень – на выполнение циклов ПДП и запрещает декодирование

адреса порта адаптера ПУ. Сигналы  , ,  , ,  , ,  (с активным низким уровнем) управляют

операциями чтения и записи данных в ячейки памяти и порты адаптера ПУ. Сигнал

«готовность канала ввода–вывода» (I/O CH RDY) устанавливается источником и

служит для согласования работы "медленных" ПУ с П. Низкий уровень

этого сигнала удлиняет цикл шины ISA (П выполняет такты ожидания). Сигнал RESET

(сброс) устанавливается П после включения источника питания и служит для

перевода ресурсов ПК в исходное (начальное) состояние. Сигналы системной

частоты 8МГц (CLK) могут быть использованы платами адаптеров ПУ. Все циклы шины

пропорциональны CLK. (с активным низким уровнем) управляют

операциями чтения и записи данных в ячейки памяти и порты адаптера ПУ. Сигнал

«готовность канала ввода–вывода» (I/O CH RDY) устанавливается источником и

служит для согласования работы "медленных" ПУ с П. Низкий уровень

этого сигнала удлиняет цикл шины ISA (П выполняет такты ожидания). Сигнал RESET

(сброс) устанавливается П после включения источника питания и служит для

перевода ресурсов ПК в исходное (начальное) состояние. Сигналы системной

частоты 8МГц (CLK) могут быть использованы платами адаптеров ПУ. Все циклы шины

пропорциональны CLK.

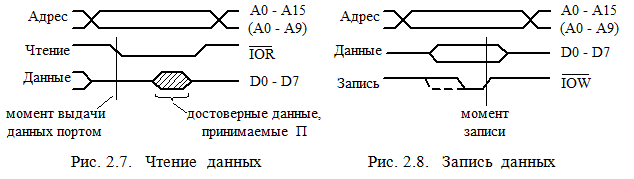

Рассмотрим

временные диаграммы обычных циклов чтения и записи данных для 8–разрядных

портов ввода–вывода (рис. 2.7 и рис. 2.8).

Шинный цикл

чтения данных реализуется каждый раз когда П выполняет команду IN (Ввод). Если

адаптер ПУ декодировал собственный адрес А0–А15 или А0–А9 (с учетом сигнала AEN=0),

то с появлением сигнала  он выдает данные на

шину D0–D7. Затем П считывает данные с шины D0–D7 до снятия сигнала он выдает данные на

шину D0–D7. Затем П считывает данные с шины D0–D7 до снятия сигнала  и линия и линия  переводится

в пассивное состояние (высокий уровень). Шинный цикл записи инициируется при

выполнении П команды OUT (Вывод). П устанавливает адрес и данные на шины А0–А15

(А0–А9) и D0–D7. Затем П формирует низкий активный уровень сигнала переводится

в пассивное состояние (высокий уровень). Шинный цикл записи инициируется при

выполнении П команды OUT (Вывод). П устанавливает адрес и данные на шины А0–А15

(А0–А9) и D0–D7. Затем П формирует низкий активный уровень сигнала  , сообщающий адаптеру, опознавшему свой

адрес с учетом сигнала AEN=0, о том, что ему следует записать информацию с шины

D0–D7. Данные гарантированно установлены за 32 нс до снятия сигнала , сообщающий адаптеру, опознавшему свой

адрес с учетом сигнала AEN=0, о том, что ему следует записать информацию с шины

D0–D7. Данные гарантированно установлены за 32 нс до снятия сигнала  и за 22 нс до появления сигнала и за 22 нс до появления сигнала  . Когда адаптер обнаруживает свой адрес,

он записывает данные с шины D0–D7 в свой порт по спаду (снятию) сигнала . Когда адаптер обнаруживает свой адрес,

он записывает данные с шины D0–D7 в свой порт по спаду (снятию) сигнала  . Адрес устанавливается за 91 нс до

появления сигнала . Адрес устанавливается за 91 нс до

появления сигнала  ( ( ). Это

время отводится на компенсацию эффекта гонок сигналов по линиям шины адреса и

декодирования адреса. Структурная схема подключения двух портов адаптера ПУ к

шине ISA мало чем отличается от структурной схемы (см. рис. 2.3). ). Это

время отводится на компенсацию эффекта гонок сигналов по линиям шины адреса и

декодирования адреса. Структурная схема подключения двух портов адаптера ПУ к

шине ISA мало чем отличается от структурной схемы (см. рис. 2.3).

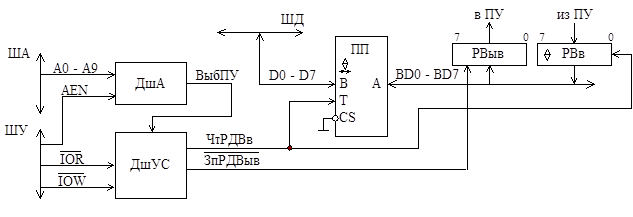

На рис. 2.9 изображена

структурная схема подключения регистров РВв и РВыв к шине ISA.

Рис. 2.9. Структурная схема подключения

РВв и РВыв к шине ISA

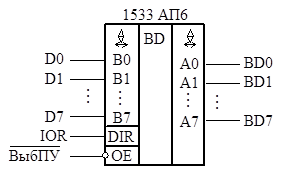

Работа схемы

описывается в соответствии с временными диаграммами (см. рис. 2.7 и 2.8) и

аналогична принципу работы схемы (см. рис. 2.3) Следует обратить внимание, что

в схеме запись в РВыв осуществляется по снятию сигнала  ,

логическая 1 на шине ISA представлена

высоким активным уровнем, выходы регистра РВв с тремя состояниями и ПП не

инвертирует сигналы данных. В качестве ПП можно использовать микросхемы 580

ВА86, 1533 АП6 и т.д. На рис. 2.10 представлены сигналы управления ПП. ,

логическая 1 на шине ISA представлена

высоким активным уровнем, выходы регистра РВв с тремя состояниями и ПП не

инвертирует сигналы данных. В качестве ПП можно использовать микросхемы 580

ВА86, 1533 АП6 и т.д. На рис. 2.10 представлены сигналы управления ПП.

Рис. 2.10. Сигналы управления ПП

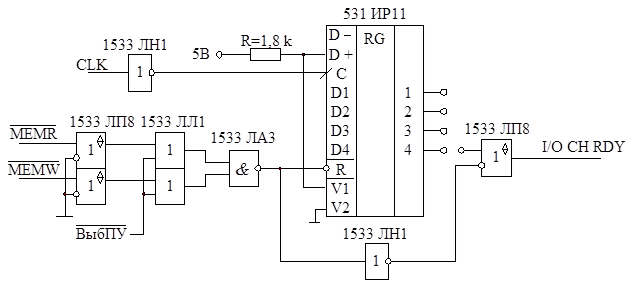

Интерфейсный

сигнал I/O CH RDY не следует путать с сигналом квитирования (например, с  ) и сигналом готовности принтера к приему

следующего символа ( ) и сигналом готовности принтера к приему

следующего символа ( или BUSY). Сигнал квитирования или BUSY). Сигнал квитирования  обязательно

вырабатывается исполнителем после каждого обращения к порту. Этот сигнал

указывает на завершение операции записи или чтения на интерфейсе. Кроме того,

сигнал обязательно

вырабатывается исполнителем после каждого обращения к порту. Этот сигнал

указывает на завершение операции записи или чтения на интерфейсе. Кроме того,

сигнал  может быть использован и для

согласования с "медленными" ПУ, как и сигнал I/O CH RDY, который является необязательным для "быстрых"

ПУ. Время ожидания активного уровня сигнала I/O CH RDY ( может быть использован и для

согласования с "медленными" ПУ, как и сигнал I/O CH RDY, который является необязательным для "быстрых"

ПУ. Время ожидания активного уровня сигнала I/O CH RDY ( ) задатчиком на интерфейсе

занимает не больше 10 машинных тактов. Появление сигнала готовности принтера в П

занимает гораздо большее время, так как работа принтера связана с его

механикой. На рис. 2.11 показана принципиальная схема формирования I/O CH RDY ( ) задатчиком на интерфейсе

занимает не больше 10 машинных тактов. Появление сигнала готовности принтера в П

занимает гораздо большее время, так как работа принтера связана с его

механикой. На рис. 2.11 показана принципиальная схема формирования I/O CH RDY ( ) при сопряжении с

"медленным" ПУ. ) при сопряжении с

"медленным" ПУ.

Рис. 2.11. Принципиальная схема формирования I/O CH RDY Рис. 2.11. Принципиальная схема формирования I/O CH RDY

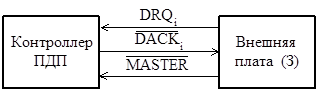

Для захвата

шины ISA внешней платой (задатчиком (З))

используются интерфейсные сигналы : запрос ПДП (DRQ ), разрешение ПДП ( ), разрешение ПДП (  ) и сигнал ведущий ( ) и сигнал ведущий ( ). На рис. 2.12 представлена схема связи контроллера

ПДП материнской платы и внешней платы для реализации цикла захвата шины. ). На рис. 2.12 представлена схема связи контроллера

ПДП материнской платы и внешней платы для реализации цикла захвата шины.

Рис. 2.12. Схема связи контроллера ПДП

и внешней платы (З)

В этом

режиме внешняя плата устанавливает сигнал DRQ , поступающий в резервный i–й канал контроллера ПДП, предварительно

запрограммированного для каскадного соединения. Контроллер ПДП выполняет

процедуру арбитража и осуществляет захват шины ISA. После этого контроллер ПДП устанавливает сигнал

разрешения , поступающий в резервный i–й канал контроллера ПДП, предварительно

запрограммированного для каскадного соединения. Контроллер ПДП выполняет

процедуру арбитража и осуществляет захват шины ISA. После этого контроллер ПДП устанавливает сигнал

разрешения   , а

внешняя плата – ответный сигнал , а

внешняя плата – ответный сигнал  , заканчивающий

процедуру захвата шины. , заканчивающий

процедуру захвата шины.

При работе с

устройствами ввода/вывода шина ISA

реализует режим доступа к 16- или 8-битному исполнителю (16- или 8-битной

внешней плате). Эти режимы имеют различные временные характеристики

интерфейсных сигналов. При разработке дешифратора адреса 16- или 8-битной

внешней платы необходимо учитывать минимальное время установки сигнала –IOR после вывода битов адреса, равное 91

нс. За это время с учетом распространения сигналов по адресной шине следует

успеть опознать (декодировать) адрес контроллера. Минимальная длительность

сигнала –IOW (-IOR) 8-битного исполнителя – 519 нс, а 16-битного

исполнителя – 176 нс. Кроме того, важным временным соотношением является

минимальное (гарантированное) время удержания данных после снятия сигнала –IOW, которое для 8-битного исполнителя

соответствует 185 нс [5]. Время появления переднего фронта сигнала –IOW не

является стандартным для разных моделей компьютеров и критическим, так как

запись данных в порт исполнителя происходит по заднему фронту сигнала –IOW.

При

обработке или формировании интерфейсных сигналов исполнителем следует учитывать

временные задержки применяемых микросхем (приемников) серии КР1533 (SN74ALS), К555 (SN74LS) и КР1554 (74AC), которые имеют следующие

соответствующие пороговые величины: 15 нс, 20 нс и 10 нс. Временная задержка

приемопередатчика КР580ВА86 равна 30 нс, КР559ИП13 – 18 нс и КР1533АП6 – 10 нс.

Стандарт

шины ISA предъявляет следующие требования к

электрическим характеристикам передатчиков, приемников и микросхем,

подключаемых к линиям этой шины. Выходной ток низкого уровня передатчиков

должен быть не менее 24 мА. Входной ток низкого уровня приемников (микросхемы)

необходим не более 0.8 мА. Этим требованиям удовлетворяют входы микросхем серии

КР1533 (SN74), КР1554 (74AC), входы/выходы А и В

приемопередатчиков КР1533АП6, входы/выходы В КР580ВА86 (КР580ВА87),

входы/выходы В КР559ИП3, входы/выходы В КР589АП16, выходы передатчиков 1533АП5,

К555АП4 и т.д. Например, приемопередатчик КР1533АП6 имеет входные/выходные токи

низкого уровня шин А и В соответственно 0.1/30 мА, которые удовлетворяют

требованиям электрических характеристик шин ISA. У микросхемы КР580ВА86 токи низкого уровня

входов/выходов В соответствуют требованиям стандарта (0.2/32 мА), а токи

низкого уровня входов/выходов А – нет (0.2/16 мА). Поэтому входы/выходы В

КР580ВА86 подключаются всегда к линиям данных шины ISA. При использовании микросхем серии К555 для

подключения к линиям шины ISA

рекомендуют использовать специальные (интерфейсные) схемы приемников, передатчиков

и приемопередатчиков с целью буферизации сигналов магистрали. Кроме того, длина

печатного проводника от контакта разъема до вывода микросхемы не должна быть

больше 65 мм и емкость любого контакта разъема относительно земли не должна

превышать 20 пФ.

Похожие материалы:

Шина USB

Шеф-инженер (Квалификационный справочник)

Шерстяное производство

Шихтовар

Шихтовщик (Часть №2 выпуска №40 ЕТКС)

Шихтовщик

|