|

В.А. Авдеев, В.Ф. Гузик

Компьютеры: шины, контроллеры, периферийные устройства

Учебное пособие. Таганрог: ТРТУ, 2001. - 536 с.

2. Системные интерфейсы

2.3. Системная шина EISA

Системная шина EISA

(расширенная промышленная стандартная архитектура) была разработана группой

фирм (Compaq, Epson, AST, NEC и т.д.) и ее основной особенностью

является то, что она является совместимой с шиной ISA. Совместимость двух шин конструктивно достигается

тем, что используется специальный разъем (слот), в котором верхний ряд

контактов соответствует шине ISA, а

нижний ряд контактов – шине EISA.

Благодаря новым функциональным и параметрическим возможностям, шина EISA используется в высокопроизводительных

системах, например, в серверах.

По сравнению с шиной ISA в шине EISA используются:

-

32 – битная шина данных и 32 – битная шина адреса;

-

централизованный системный арбитр с фиксированным или циклическим

приоритетом, обеспечивающий приоритетный доступ к шине задатчиков, процессоров,

устройств ПДП с помощью контроллера ПДП и контроллера регенерации динамической

памяти;

-

расширенная подсистема ПДП с 8-, 16- и 32-битными передачами данных со

скоростью до 33 Мбайт в секунду;

-

радиальный способ выбора каждого слота внешних плат, что позволяет реализовать

режим автоконфигурации компонентов системы;

-

линии прерывания с сигналами запросов, действующих по фронту или по

уровню (линия запроса по уровню позволяет подключить несколько устройств);

-

различные режимы передачи данных (стандартный, пакетный и сжатый). Режимы

передачи данных определяют соответствующие структуры данных, указанные в морфологической

графе классификации интерфейсов.

Таким образом, шина EISA продолжает

традиционный путь развития системных интерфейсов: увеличение числа линий связи

(линий данных, адреса и управления), расширение функций арбитража, ПДП,

прерывания и реализацию режима автоконфигурации (технологии Plug

& Play, чтобы исключить конфликт ресурсов на

главной ЭВМ и использование перемычек (переключателей) для настройки системы на

этапе ее инициализации).

Рассмотрим назначение дополнительных к шине ISA следующих сигналов:

-

AENi (i = 0, 1, …, 15). Сигнал разрешения адреса, используемый для

выбора i-го слота на системной плате (каждая i-ая радиальная линия связана с контактом AENi слота). С помощью этого сигнала осуществляется выбор

требуемой внешней платы во время автоконфигурирования системы;

-

(BE3 – BE0)#. Сигналы

разрешения байтов (формируемые процессором) низкими активными уровнями

определяют в текущем цикле используемые байты на 32-битной шине данных, например,

BE0# = 0 указывает на байт D0-D7, а BE3# = 0 – на байт D31- D24;

-

CMD#. Сигнал строба окончания команды,

устанавливаемый процессором и применяемый вместе с сигналом START#

для выполнения сжатых циклов на шине. Этот сигнал формируется по положительному

сигналу BCLK, если сброшен сигнал START#,

и удерживается до конца цикла шины;

-

EXRDY. Сигнал готовности исполнителя EISA, указывающий на завершение цикла передачи данных.

Отсутствие этого сигнала на соответствующем входе задатчика вызывает в его

работе появление тактов ожидания;

-

EX32# и EX16#. Сигналы,

соответственно, 32-битного и 16-битного исполнителей EISA,

которые вырабатываются в начале цикла шины. Сигналы EX32#

и EX16# анализируются 32-битным задатчиком с целью

организации дополнительных циклов на шине в случае необходимости. Если

указанные сигналы не установлены на шине, то задатчик определяет это как

наличие 8-битного исполнителя и организует четыре цикла на шине для передачи

32-битных данных. Для 8- и 16-битных исполнителей сигнал EX32#

задатчика указывает исполнителям о завершении обмена данными;

-

LOCK# (Блокировка). Сигнал длительностью не

более 8 мкс, устанавливаемый задатчиком при получении исключительного доступа к

шине при обращении к памяти или устройству ввода-вывода;

-

MREQi# (Запрос от i-го

задатчика). Сигнал задатчика, поступающий на соответствующий вход системного

арбитра, синхронизируется BCLK и сохраняется до прихода

MACKi#.

-

MACKi# (Подтверждение запроса). Этим

сигналом системный арбитр сообщает i-му задатчику о

разрешении доступа к шине, синхронизируется BCLK и

удерживается до снятия сигнала MREQi#.

-

START# (Старт). Сигнал, равный по длительности

одному периоду BCLK и устанавливаемый задатчиком для

определения начала цикла передачи данных;

-

MS BURST#

(Пакетный режим задатчика). Этот сигнал устанавливается задатчиком и сообщает

исполнителю о режиме пакетной передачи. Сигнал MS BURST# формируется по переднему

фронту BCLK после выдачи сигнала START#

и при наличии сигнала SL BURST#, приходящего от исполнителя;

-

SL BURST#

(Пакетный режим исполнителя). Сигнал, сообщающий задатчику о том, что

исполнитель поддерживает пакетный режим;

-

M/IO# (память /

ввод-вывод). Используется задатчиком для уведомления устройств о типе цикла

шины (1- цикл передачи данных в память или 0 – цикл передачи данных в

устройство ввода / вывода);

-

W/R# (Запись / чтение).

Высокий уровень сигнала указывает на запись данных, а низкий уровень – на

чтение данных;

-

LA2 – LA16, LA24 – 31 (Адресная шина). Сигналы соответствующих битов

адреса, устанавливаемые задатчиком и не фиксируемые в течение всего цикла

обмена данными. Адресные сигналы LA1 и LA0 не используется, и вместо них применяются сигналы (BE3 – BE0)#;

-

D16 – D31 Сигналы

старших битов данных.

Различают следующие режимы передачи данных: стандартный,

пакетный и сжатый, выполняемый только процессором. В стандартном режиме

используются тактовые сигналы BCLK, частота которых

находится в диапазоне от 6 до 8,33 МГц и зависит от частоты микропроцессора,

например, для микропроцессора с частотой 25 МГц частота EISA

равна 8,33 МГц.

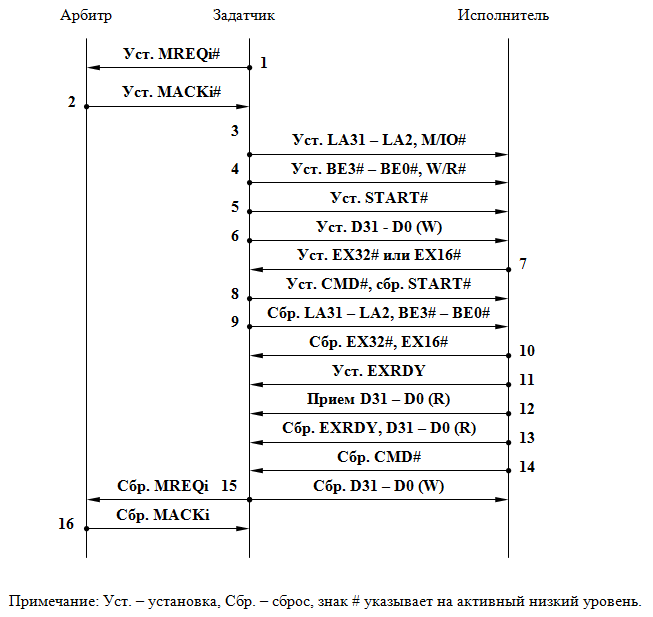

Последовательность сигналов стандартной передачи показана на

рис. 2.13.

Рис. 2.13. Последовательность сигналов стандартной

передачи данных

Установка сигналов в указанной последовательности

производится по положительному фронту сигнала BCLK.

При выполнении стандартной передачи осуществляются следующие

действия:

1. Задатчик устанавливает сигнал MREQi #, поступающий в арбитр, для получения управления

шиной EISA.

2. Арбитр выполняет процедуру арбитража и отвечает сигналом MACKi #.

3. Задатчик, захватив шину, устанавливает адрес LA31 – LA2 и сигнал исполнителя M/IO по положительному фронту BCLK.

4. Затем захватчик указывает тип операции сигналом W/R# и разрешенные байты сигналами BE3# - BE0#.

5. По положительному фронту BCLK

задатчик формирует сигнал начала цикла на шине START#.

6. Если выполняется операция записи (W)

данных в исполнитель, то задатчик устанавливает по положительному фронту BCLK данные D31 – D0.

7. Исполнитель после дешифрации адреса отвечает сигналом EX32# (EX16#), указывающим задатчику

на разрядность исполнителя.

8. Задатчик анализирует сигнал EX32#(EX16#), сбрасывает сигнал START# и

устанавливает сигнал CMD#.

9. Задатчик сбрасывает биты адреса LA31

– LA2 и сигналы BE3# – BE0#, кроме того, по отрицательному фронту BCLK

задатчик выполняет проверку сигнала готовности исполнителя EXRDY

(при его отсутствии производятся такты ожидания в работе задатчика).

10. В свою очередь, исполнитель снимает сигнал EX32#(EX16#) и устанавливает сигнал

готовности EXRDY, который прекращает такты ожидания в

работе задатчика.

11. Если выполняется операция чтения (R),

то при наличии сигнала EXRDY задатчик осуществляет

прием данных D31 – D0, которые

уже были установлены исполнителем при условии опознания адреса и наличия низких

уровней сигналов W/R# и CMD#.

12,13. Исполнитель сбрасывает сигнал EXRDY

и снимает данные D31 – D0 при выполнении

операции чтения (R).

14. Задатчик завершает цикл одиночной передачи данных,

сбрасывает сигнал MREQi # и снимает данные D31 – D0, если выполнялась операция (W) записи данных.

15. Арбитр сбрасывает сигнал MACKi

#.

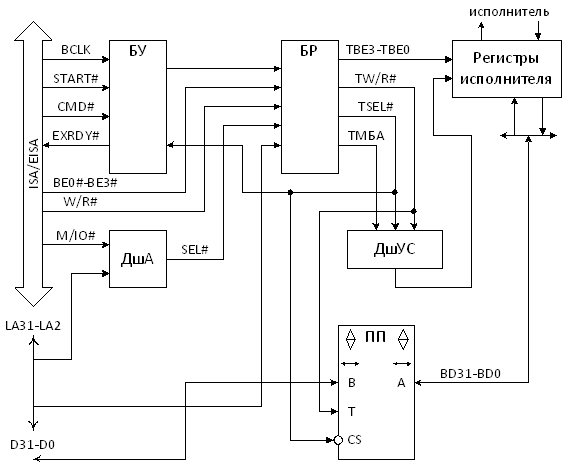

На рис. 2.14 представлена обобщенная структурная схема

исполнителя.

С целью упрощения рисунка структурной схемы в ней не показаны

компоненты автоконфигурирования.

Рис. 2.14. Обобщенная

структурная схема исполнителя

Так

как частота BCLK является невысокой (максимальная

частота равна 8,33 МГц), то возможна предварительная дешифрация старших битов

адреса (СБА) с учетом сигнала M/IO# дешифратором адреса (ДшА), причем

сигнал опознания адреса SEL

запоминается в триггере буферного регистра (БР). Сигналы LA31 – LA2, W/R# и BE3# - BE0#

не защелкиваются на системной плате и не сохраняются в течение цикла шины,

поэтому их необходимо запоминать в БР по сигналу блока управления (БУ). БУ,

кроме того, формирует сигнал готовности EXRDY и сигнал сброса БР.

Младшие

биты адреса (МБА), предназначенные для выбора регистров исполнителя, также

фиксируются в БР. Дешифратор управляющих сигналов (ДшУС) с учетом запомненных

сигналов TW/R#, TSEL#

и ТМБА вырабатывает сигналы записи и чтения соответствующих регистров выбранного

исполнителя. Для подключения регистров исполнителя к шине D31 – D0 употребляется приемопередатчик (ПП), с помощью которого

осуществляется управление направлением передачи данных.

Пакетный

режим повторяет последовательность действий одиночной передачи и отличается от

одиночной передачи тем, что после сброса сигнала START выполняются следующие события.

Задатчик

анализирует по отрицательному фронту BCLK сигналы EXRDY и SLBURST# и устанавливает сигнал MSBURST#.

Данные

задатчика являются достоверными сразу после появления сигнала START#, а данные, передаваемые

исполнителем, действительны до снятия сигнала CMD#.

Цикл

пакетной передачи данных завершается снятием сигналов CMD# и MSBURST#.

В течение этого цикла задатчик каждый раз устанавливает новые значения LA31 – LA2, M/IO#, BE3# – BE0#, W/R# и данные при записи их в порт исполнителя или выполняет

прием данных исполнителя в режиме чтения, т.е. реализуется многофазная передача

адреса и данных.

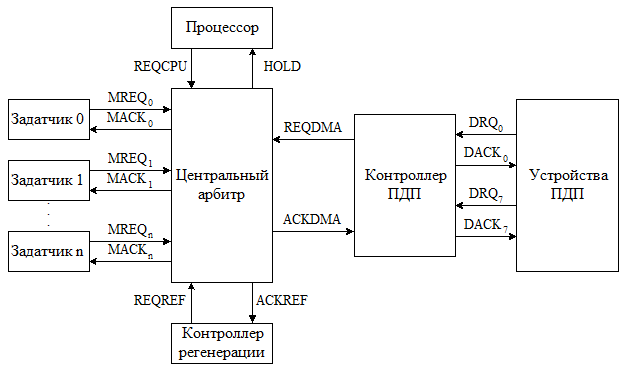

Тип

задатчика EISA или ISA определяется с помощью сигналов арбитража: в шине EISA используются сигналы MREQi# и MACKi#, а в шине ISA – сигналы DRQi и DACKi. На рис. 2.15 изображена структурная схема центрального

арбитража.

Рис. 2.15.

Структурная схема центрального арбитража

Приоритет

устройств, подключаемых к центральному арбитру, определяется в порядке

убывания: контроллер, контроллер ПДП, процессор и задатчики.

В системе с шиной EISA употребляются

7 каналов ПДП, поддерживающие 8-, 16- и 32-битные режимы передачи данных.

Различают следующие типы циклов ПДП: ISA – совместимый

цикл, выполняющий одну передачу данных за 8 тактов шины; циклы типа А,

содержащие 6 тактов шины; циклы типа В, реализуемые за 4 такта, и циклы типа С,

обеспечивающие передачу за один такт шины.

Передачи типа С (пакетные передачи) обеспечиваются

использованием положительного и отрицательного фронтов сигнала BCLK, т.е. в течение первого полупериода происходит чтение

данных, а затем в течение второго полупериода их запись. Передача типа С

используется только специальными платами EISA с

жесткими временными требованиями. Этот тип передачи ограничивается областью

памяти в 1 Кбайт, т.е. используется только 10 младших битов адреса.

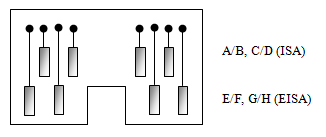

Как уже указывалось, конструктивно слот шины EISA позволяет использовать внешние платы шины ISA. На рис. 2.16 показана контактная часть платы расширения

шины ISA со стороны контактных рядов А и С, а контактные

ряды B и D расположены на

другой стороне платы.

Рис.

2.16. Контактная часть

платы шины ISA

Контакты А1 – А31 (В1 – В31) относятся к шине расширения PC/XT, а контакты C1

– C18 (D1 – D18)

являются дополнением и в общей совокупности составляют контакты шины расширения

ISA. С целью снижения действия помех в конструкции шины

ISA линии основных сигналов отделены от линий питания,

расположенных на контактных сторонах B и D.

Различают два типа внешних плат: 8-битная (короткие с

контактами A и B) и 16-битные,

вставляемые в двухрядный слот.

Контактная часть фрагмента платы шины EISA

представлена на рис. 2.17.

Рис.

2.17. Контактная часть фрагмента разъема платы шины EISA

Из рисунка видно, что контактные ряды E/F и G/H,

соответствующие шине EISA, расположены ниже контактных

рядов A/B и C/D шины ISA. Ключевая прорезь между

ламелями EISA позволяет совместить двухрядные

контактные ряды слота и вставленной платы шин ISA и EISA.

Номера контактов и названия сигналов слота ISA/EISA показаны в табл. 2.1 и 2.2.

Таблица

2.1

|

НОМЕР

|

РЯД А

|

РЯД В

|

РЯД Е

|

РЯД F

|

|

1

|

2

|

3

|

4

|

5

|

|

1

|

IOCHK

|

GND

|

CMD#

|

GND

|

|

2

|

DATA7

|

RESET

|

START#

|

+5B

|

|

3

|

DATA6

|

+5B

|

EXRDY

|

+5B

|

|

4

|

DATA5

|

IRQ 2/9

|

EX32#

|

UNUSED

|

|

5

|

DATA4

|

-5B

|

GND

|

UNUSED

|

|

6

|

DATA3

|

DRQ2

|

KEY

|

KEY

|

|

7

|

DATA2

|

-12B

|

EX16#

|

UNUSED

|

|

8

|

DATA1

|

OWS#

|

SLBURST#

|

UNUSED

|

|

9

|

DATA0

|

+12B

|

MSBURST#

|

+12B

|

|

10

|

IOCHRDY

|

GND

|

W/R#

|

M/IO#

|

|

11

|

AEN

|

SMEMW#

|

GND

|

LOCK#

|

|

12

|

ADDR19

|

SMEMR#

|

EMB66#

|

RESERVED

|

|

13

|

ADDR18

|

IOW#

|

EMB133#

|

GND

|

|

14

|

ADDR17

|

IOR#

|

RESERVED

|

RESERVED

|

|

15

|

ADDR16

|

DACK3#

|

GND

|

BE3#

|

|

16

|

ADDR15

|

DRQ3

|

KEY

|

KEY

|

|

17

|

ADDR14

|

DACK1#

|

BE1#

|

BE2#

|

|

18

|

ADDR13

|

DRQ1

|

LA31

|

BE0#

|

|

19

|

ADDR12

|

REFR#

|

GND

|

GND

|

|

20

|

ADDR11

|

BCLK

|

LA30

|

+5B

|

|

21

|

ADDR10

|

IRQ7

|

LA28

|

LA29

|

|

22

|

ADDR9

|

IRQ6

|

LA27

|

GND

|

|

23

|

ADDR8

|

IRQ5

|

LA25

|

LA26

|

|

24

|

ADDR7

|

IRQ4

|

GND

|

LA24

|

|

25

|

ADDR6

|

IRQ3

|

KEY

|

KEY

|

|

26

|

ADDR5

|

DACK2#

|

LA15

|

LA16

|

|

27

|

ADDR4

|

TC

|

LA13

|

LA14

|

|

28

|

ADDR3

|

BALE

|

LA12

|

+5B

|

|

29

|

ADDR2

|

+5B

|

LA11

|

+5B

|

|

30

|

ADDR1

|

OSC

|

GND

|

GND

|

|

31

|

ADDR0

|

GND

|

LA9

|

LA10

|

Таблица

2.2

|

НОМЕР

|

ряд

с

|

ряд

D

|

ряд

g

|

ряд

H

|

|

1

|

SBHE#

|

MCS16#

|

LA7

|

LA8

|

|

2

|

LA23

|

IOCS16#

|

GND

|

LA6

|

|

3

|

LA22

|

IRQ10

|

LA4

|

LA5

|

|

4

|

LA21

|

IRQ11

|

LA3

|

+5B

|

|

5

|

LA20

|

IRQ12

|

GND

|

LA2

|

|

6

|

LA19

|

IRQ15

|

KEY

|

KEY

|

|

7

|

LA18

|

IRQ14

|

DATA17

|

DATA16

|

|

8

|

LA17

|

DACK0#

|

DATA19

|

DATA18`

|

|

9

|

MEMR#

|

DRQ0

|

DATA20

|

GND

|

|

10

|

MEMW#

|

DACK5#

|

DATA22

|

DATA21

|

|

11

|

DATA8

|

DRQ5

|

GND

|

DATA23

|

|

12

|

DATA9

|

DACK6#

|

DATA25

|

DATA24

|

|

13

|

DATA10

|

DRQ6

|

DATA26

|

GND

|

|

14

|

DATA11

|

DACK7#

|

DATA28

|

DATA24

|

|

15

|

DATA12

|

DRQ7

|

KEY

|

KEY

|

|

16

|

DATA13

|

+5B

|

GND

|

DATA29

|

|

17

|

DATA14

|

MASTER#

|

DATA30

|

+5B

|

|

18

|

DATA15

|

GND

|

DATA31

|

+5B

|

|

19

|

|

|

MREQ#

|

MACK#

|

Похожие материалы:

Системная постановка прямых продаж

Систематизация правовой информации (Под ред. Баранов П.П., 2006)

Систематизация правовой информации

Системные подходы к управлению инновационной деятельностью компаний. Выводы

Системный анализ (Алесинская Т.В.)

Системный интерфейс MULTIBUS

|