|

В.А. Авдеев, В.Ф. Гузик

Компьютеры: шины, контроллеры, периферийные устройства

Учебное пособие. Таганрог: ТРТУ, 2001. - 536 с.

2. Системные интерфейсы

2.4. Интерфейс с совмещенной шиной

С целью

ограничения числа выводов схемы кристалла и (или) уменьшения числа линий связи

используют шины с совмещенной передачей адреса и данных. Рассмотрим общий

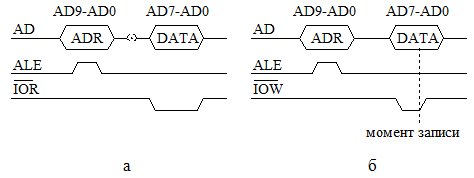

принцип построения интерфейса ввода/вывода для такого случая. На рис. 2.18.

представлены временные диаграммы циклов ввода (а) и вывода (б) совмещенной

шины.

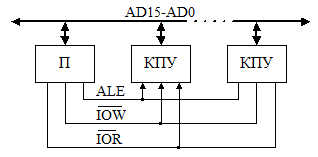

Схема соединения компонентов системы, содержащей

совмещенную шину, показана на рис. 2.19.

Принцип

функционирования системы с совмещенной шиной происходит в соответствии с

временными диаграммами см. на рис. 2.18 а и б. Процессор (П) направляет адрес (ADR) по шине AD, доступный всем контроллерам ПУ (КПУ). С целью упрощения

схем используется 10-битный двоичный адрес порта КПУ и байтовая передача данных

(DATA). Затем П устанавливает сигнал разрешения

фиксации адреса (ALE). Этот сигнал

необходим в КПУ для запоминания адреса в регистре – защелке при употреблении

быстродействующей совмещенной шины или для запоминания сигнала дешифрации старшей

части адреса, выбирающего ПУ, и младших битов адреса, необходимых для

идентификации порта в КПУ.

Рис. 2.18. Временные диаграммы циклов

ввода (а) и вывода (б)

Рис. 2.19. Схема соединения

компонентов системы с совмещенной шиной

Если

выполняется цикл ввода данных, то П устанавливает сигнал чтение данных ( ), по которому выбранное в

соответствии с адресом КПУ выдает данные (DATA) на шину AD. Знаком (×) показано переключение направления передачи информации на шине AD, т.е. вначале адрес направляется из

П, а потом данные поступили в П. ), по которому выбранное в

соответствии с адресом КПУ выдает данные (DATA) на шину AD. Знаком (×) показано переключение направления передачи информации на шине AD, т.е. вначале адрес направляется из

П, а потом данные поступили в П.

В случае

цикла вывода процессор устанавливает на шине AD адрес и данные. КПУ, которое опознало собственный адрес, при

поступлении сигнала  запоминает данные в соответствующем порте. запоминает данные в соответствующем порте.

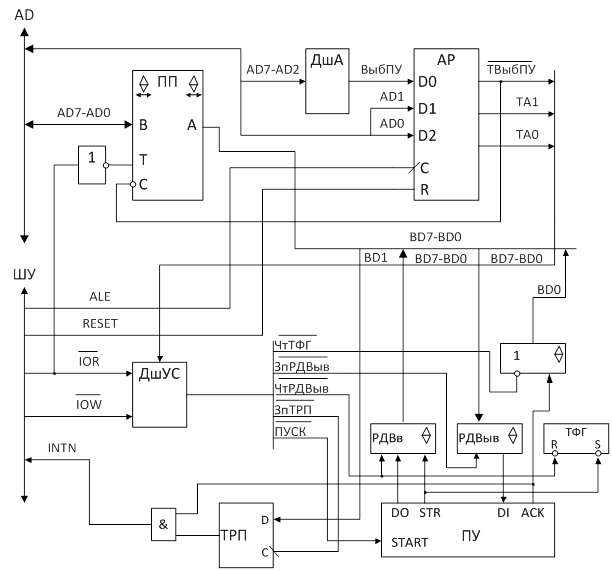

На рис. 2.20

изображена структурная схема контроллера программного обмена (КПУ), подключенного

к совмещенной шине.

Рис. 2.20. Структурная схема

контроллера программного обмена

Процессор

через совмещенную шину и порты контроллера осуществляет управление работой ПУ.

В табл. 2.3 приведены адреса и тип доступа соответствующих портов контроллера.

Таблица 2.3

|

Порты

|

Доступ

|

Адрес

|

|

РДВв

|

R

|

2F5h

|

|

РДВыв

|

W

|

|

ТФГ

|

R

|

2F6h

|

|

Пуск

|

W

|

|

ТРП

|

W

|

2F7h

|

Примечание: R – чтение, W –

запись

Общий принцип

взаимодействия компонентов системы следующий. Процессор выводит байт данных в

РД Выв (2F5h). Затем процессор делает вывод без передачи данных по адресу

2F6h. В результате выполнения этой операции ДшУС формирует сигнал

Пуск, который осуществляет запуск ПУ на выполнение соответствующей работы.

После завершения работы ПУ передает результат в РД Вв и записывает его по

сигналу строб (STR), который

одновременно устанавливает триггер флага готовности (ТФГ). Процессор путем

опроса ТФГ (2F6h) или через прерывание (предварительно со стороны процессора

установлен триггер разрешения прерывания (ТРП), порт 2F7h) узнает, что

РДВв полон, и считывает (вводит) из него байт данных в свой внутренний регистр,

причем при чтении сбрасывается триггер ТФГ.

При записи

или чтении данных во время адресной части цикла процессор, как уже отмечалось,

устанавливает адрес, например, 2F5h. Старшая (общая для всех портов)

часть адреса AD7-AD2 декодируется ДшА, который после опознания собственного

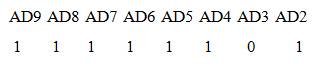

адреса формирует на выходе сигнал  . Двоичный эквивалент AD9-AD2 – 11111101. . Двоичный эквивалент AD9-AD2 – 11111101.

После этого

процессор устанавливает сигнал ALE,

который осуществляет запись сигнала  и младших битов

адреса AD1 и AD0, выполняющих выбор портов внутри контроллера, в 3-битовый

адресный регистр АР. Необходимость запоминания этих трех сигналов связана с

тем, что после адреса процессор выводит данные (в цикле записи), которые через

ПП поступают на входы РДВыв. В этот момент времени ПП открыт в направлении с В

на А, так как сигнал и младших битов

адреса AD1 и AD0, выполняющих выбор портов внутри контроллера, в 3-битовый

адресный регистр АР. Необходимость запоминания этих трех сигналов связана с

тем, что после адреса процессор выводит данные (в цикле записи), которые через

ПП поступают на входы РДВыв. В этот момент времени ПП открыт в направлении с В

на А, так как сигнал  отсутствует и на входе Т приемопередатчика установлен низкий уровень.

Если Т=0, то направление передачи с В на А (В®А). И только при чтении данных ПП разрешает передачу

данных с А на В (А®В).

Запись данных в РД Выв выполняется при установке процессором сигнала отсутствует и на входе Т приемопередатчика установлен низкий уровень.

Если Т=0, то направление передачи с В на А (В®А). И только при чтении данных ПП разрешает передачу

данных с А на В (А®В).

Запись данных в РД Выв выполняется при установке процессором сигнала  . При этом на выходе ДшУС формируется

сигнал ЗпРДВыв при наличии сигналов: . При этом на выходе ДшУС формируется

сигнал ЗпРДВыв при наличии сигналов:  , ,  , ТА1=0 и ТА0=1. Аналогичным образом

осуществляется чтение, например, РДВв. О том, что содержимое РДВв введено в процессор,

ПУ определяет по сигналу АСК (выходу ТФГ). Если ТФГ сброшен, то РДВв уже пуст. Функциональная

схема ДшА, АР и УС изображена на рис. 2.21. , ТА1=0 и ТА0=1. Аналогичным образом

осуществляется чтение, например, РДВв. О том, что содержимое РДВв введено в процессор,

ПУ определяет по сигналу АСК (выходу ТФГ). Если ТФГ сброшен, то РДВв уже пуст. Функциональная

схема ДшА, АР и УС изображена на рис. 2.21.

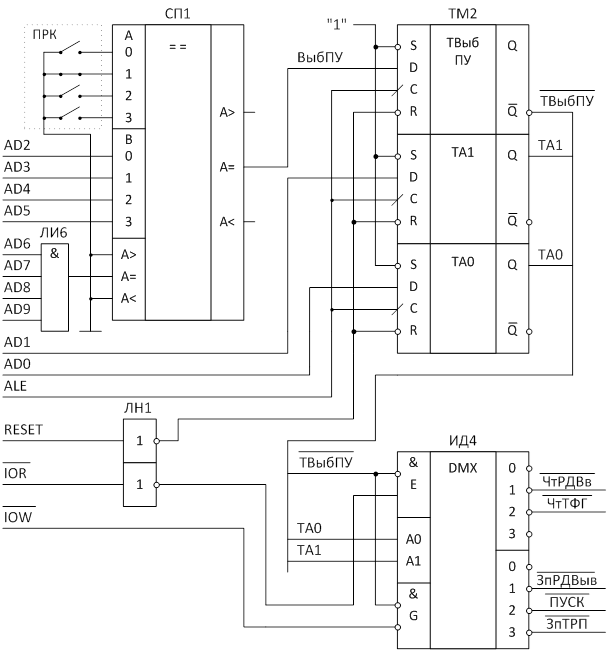

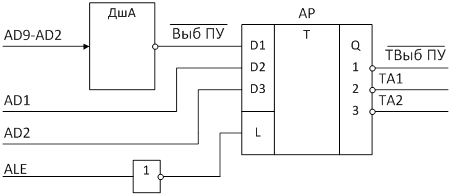

Рис. 2.21. Функциональная схема ДшА,

АР и ДшУС

Схема ДшА

реализована на элементах СП1 и ЛИ6 и декодирует общую старшую часть адреса AD9-AD2. Адресный регистр (АР) выполнен на трех триггерах ТМ2, а

дешифратор управляющих сигналов (ДшУС) – на демультиплексоре (DMX). Схема сравнения СП1 содержит переключатели

(ПРК), которые позволяют изменять диапазон значений четырех битов адреса AD5-AD2. Схема ДшА декодирует двоичный код, представленный на рис.

2.22.

Рис. 2.22. Двоичный код старшей части

адреса

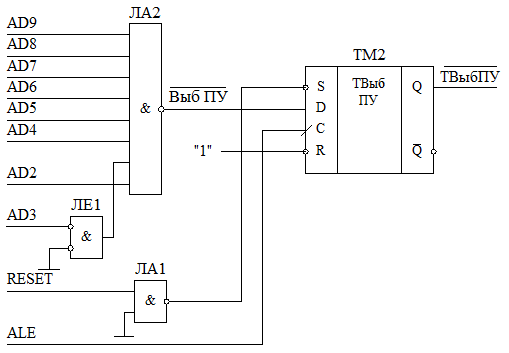

На рис. 2.23

показана схема ДшА, которая формирует сигнал ВыбПУ низким активным уровнем.

Этот сигнал запоминается в триггере  , предварительно

установленного сигналом RESET

в единичное состояние. , предварительно

установленного сигналом RESET

в единичное состояние.

Рис. 2.23. Схема ДшА и ТВыбПУ с

запоминанием сигнала

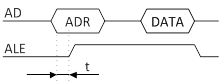

В том

случае, если сигнал ALE установлен на

все время цикла ввода или вывода (рис. 2.24), то можно для реализации АР

использовать триггеры – защелки (регистры), запоминающие сигналы на входах D по уровню управляющего сигнала,

поступающего на вход загрузки L.

Рис. 2.24 Временная диаграмма цикла

ввода(вывода), определяемого сигналом ALE

Следует

отметить, что сигнал ALE

устанавливается процессором через время t после того, как выдан адрес (за это время гарантированно

завершается дешифрация адреса). На рис. 2.25 показана схема запоминания

сигналов  , DA1 и DA0 с

помощью D – L триггеров. , DA1 и DA0 с

помощью D – L триггеров.

Рис. 2.25. Схема запоминания адресных

сигналов с помощью D – L триггеров

Фиксация

сигналов в АР происходит до появления сигнала ALE, а с его установкой запрещается запись сигналов в АР.

Схема ДшУС (см. рис. 2.21) функционирует в соответствии с табл. 2.4.

Таблица 2.4

|

|

AD1

|

AD0

|

|

|

Операция (сигнал ДшУс)

|

|

0

|

0

|

1

|

0

|

1

|

|

|

0

|

1

|

0

|

0

|

1

|

|

|

0

|

0

|

1

|

1

|

0

|

|

|

0

|

1

|

0

|

1

|

0

|

|

|

0

|

1

|

1

|

1

|

0

|

|

Похожие материалы:

Интерфейс CAMAC

Интересы, страхование которых не допускается - ст.928 ГК РФ

Интервальный кластер-анализ

Интерфейсы НЖМД

Интонировщик (Выпуск №59 ЕТКС )

Инфляция и безработица

|