|

В.А. Авдеев, В.Ф. Гузик

Компьютеры: шины, контроллеры, периферийные устройства

Учебное пособие. Таганрог: ТРТУ, 2001. - 536 с.

3. Способы обмена данными

3.3. Прямой доступ к памяти

Обмен

в режиме ПДП является наиболее быстродействующим и требующим значительных

аппаратурных затрат. В режиме ПДП обмен данными выполняется между ПУ и ОП без

участия П и реализуется аппаратурным способом. В этом режиме П используется для

инициализации (подготовки) контроллера ПДП. Режим ПДП обычно применяется для

организации связи внешней памяти с ОП для передачи блоков данных. Контроллер

ПДП (КПДП) в этом режиме захватывает интерфейс, направляет адрес ячейки в ОП,

подсчитывает количество передаваемых байтов (слов), вырабатывает необходимые

интерфейсные сигналы как задатчик и координирует свою работу с работой

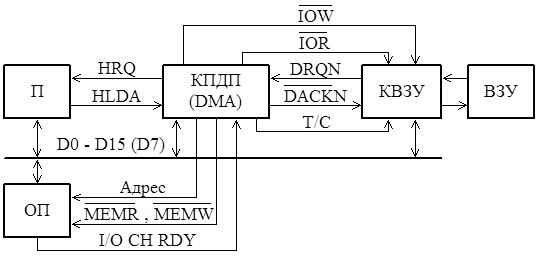

контроллера внешней памяти (ВЗУ). На рис. 3.10 представлена схема сопряжения П,

КПДП, контроллера ВЗУ (КВЗУ) и ВЗУ в режиме ПДП.

Рис. 3.10. Схема сопряжения устройств

в режиме ПДП

В

начале режима ПДП П инициализирует КПДП: задает режим работы, передает

начальный (стартовый) адрес ОП, число передаваемых байтов (слов) и т.д. Затем П

выводит команды в КВЗУ, указывающие тип операции (запись, чтение или поиск и

так далее). После подготовки данных КВЗУ устанавливает сигнал запрос ПДП (DMA)

DRQ N (N – номер канала). КПДП (микросхема i8237) содержит 4 канала, работающие

в режиме разделения времени.

В

свою очередь, КПДП формирует сигнал запрос шины HRQ, поступающий в П. П освобождает

интерфейс (переводит свои выходы в состояние выключено) и устанавливает сигнал подтверждения

шины HLDA.

С

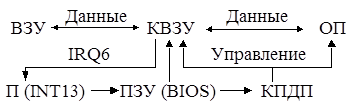

этого момента времени задатчиком на интерфейсе становится КПДП, под управлением

которого осуществляется передача данных через КВЗУ между ВЗУ и ОП по следующей

схеме (рис. 3.11).

Рис. 3.11. Схема выполнения режима

ПДП

Если в качестве ВЗУ используется накопитель гибких магнитных

дисков (НГМД), то служебные функции базовой системы ввода–вывода (BIOS),

управляющие работой дискеты и хранящиеся в ПЗУ, вызываются программным

прерыванием INT 13H.

После

захвата интерфейса КПДП передает в КВЗУ сигнал подтверждения ПДП  N, определяющий начало передачи данных.

Сигнал Т/С (окончание счета) устанавливается КПДП после окончания счета числа

пересылок данных. ПК PC/AT имеет 7 каналов ПДП (каскадное соединение двух

микросхем i8237), причем каналы 0–3 поддерживают передачу только 8–разрядных данных,

а каналы 5–7 – 16–разрядных данных. Канал 0 в ПК PC/ХT предназначен для

регенерации динамической памяти, а канал 2 – для дисковых операций. N, определяющий начало передачи данных.

Сигнал Т/С (окончание счета) устанавливается КПДП после окончания счета числа

пересылок данных. ПК PC/AT имеет 7 каналов ПДП (каскадное соединение двух

микросхем i8237), причем каналы 0–3 поддерживают передачу только 8–разрядных данных,

а каналы 5–7 – 16–разрядных данных. Канал 0 в ПК PC/ХT предназначен для

регенерации динамической памяти, а канал 2 – для дисковых операций.

Последовательность

основных действий устройств в режиме ПДП при чтении байта данных из ОП (см.

рис. 3.10) следующая: КВЗУ (КНГМД) формирует сигнал DRQ 2; КПДП вырабатывает сигнал

HRQ; П освобождает шину и устанавливает сигнал HLDA; КПДП, захватив шину,

передает адрес в ОП; КПДП формирует сигнал  2,

поступающий в КНГМД; КПДП вырабатывает сигнал 2,

поступающий в КНГМД; КПДП вырабатывает сигнал  ,

осуществляющий чтение выбранной ячейки ОП; содержимое ячейки ОП запоминается в

регистре данных КНГМД по сигналу ,

осуществляющий чтение выбранной ячейки ОП; содержимое ячейки ОП запоминается в

регистре данных КНГМД по сигналу  , установленному КПДП;

КПДП снимает сигнал HRQ (режим одиночной передачи); П сбрасывает сигнал HLDA;

КПДП увеличивает на 1 значение адреса и уменьшает на 1 число передаваемых

байтов данных с появлением сигнала I/O CH RDY из ОП. Если число передаваемых

байтов не равно FFFFh, то последовательность действий повторяется до тех пор,

пока не будет сформирован сигнал T/C. Сигнал Т/С используется для формирования

сигнала прерывания IRQ 6 (при наличии сигнала разрешения прерывания),

сообщающего П о завершении передачи блока данных. В ПК РС/ХТ и РС/АТ в качестве

КПДП применяется микросхема i8237 (отечественный аналог 1810 ВТ37). , установленному КПДП;

КПДП снимает сигнал HRQ (режим одиночной передачи); П сбрасывает сигнал HLDA;

КПДП увеличивает на 1 значение адреса и уменьшает на 1 число передаваемых

байтов данных с появлением сигнала I/O CH RDY из ОП. Если число передаваемых

байтов не равно FFFFh, то последовательность действий повторяется до тех пор,

пока не будет сформирован сигнал T/C. Сигнал Т/С используется для формирования

сигнала прерывания IRQ 6 (при наличии сигнала разрешения прерывания),

сообщающего П о завершении передачи блока данных. В ПК РС/ХТ и РС/АТ в качестве

КПДП применяется микросхема i8237 (отечественный аналог 1810 ВТ37).

Режим

прямого доступа к памяти предназначен для передачи блоков данных между оперативной

памятью и периферийным устройством (внешней платой). В этом режиме КПДП

управляет работой шины, т.е. является задатчиком, а оперативная память –

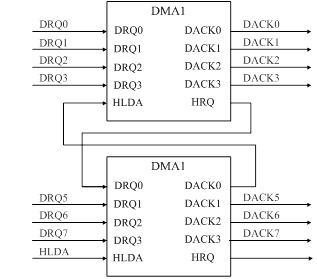

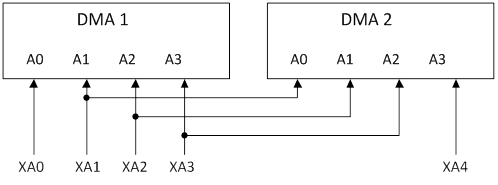

исполнителем. В PC/AT для реализации режима ПДП используются 2 микросхемы I8237

(DMA), соединенные каскадно (рис. 3.12.) с целью увеличения числа каналов.

Рис. 3.12. Каскадное соединение DMA1

и DMA2

Каждая микросхема DMA содержит 4 канала (К0-К3), работающих в

режиме разделения времени (в какой-либо момент времени только один канал

является активным и обслуживает подключенное к нему периферийное устройство).

Наивысшим приоритетом обладает канал 0 (К0). С увеличением номера канала

приоритет уменьшается. Всякому каналу соответствует сигнал DRQN (N=0-3) ,

называемый запросом ПДП, т.е. периферийное устройство, требующее режима ПДП,

устанавливает этот сигнал. Здесь усматривается некоторая аналогия с сигналами

запросов прерывания. Если одновременно поступает несколько сигналов запросов

ПДП, то внутренняя схема арбитража в DMA выбирает наиболее приоритетный сигнал

DRQN. После этого DMA устанавливает общий для всех каналов сигнал HRQ (запрос

шины) и после поступления от процессора сигнала HLDA (подтверждения на захват

шины) DMA становится задатчиком и формирует для N-го периферийного устройства

сигнал DACKN (подтверждение ПДП), разрешающий циклы ПДП. Для двух

каскадно-соединенных DMA наивысший приоритет имеет сигнал DRQ0, а сигнал DRQ7 –

наименьший. Кроме того, для реализации каскадного соединения четвертый по

общему счету канал в DMA2 используется только для этой цели (его необходимо

запрограммировать на выполнение режима каскадирования). Назначение каналов КПДП

в PC/AT представлено в табл. 3.3.

Таблица 3.3

|

Каналы

|

Назначение

|

|

К0

|

Резерв для PC/AT, регенерация памяти для PC/XT

|

|

К1

|

Резерв

|

|

К2

|

Работа с контроллером НГМД

|

|

К3

|

Резерв или для некоторых типов ПК работа с жестким

диском

|

|

К4

|

Каскадирование

|

|

К5

|

Резерв

|

|

К6

|

Резерв

|

|

К7

|

Резерв

|

Каналы К0-К3 используются для байтовых передач данных, а

каналы К5-К7 – для передачи 16-битовых слов. Внешние платы (задатчики)

употребляют резервные каналы для получения доступа к системной шине. Для выполнения

этой цели внешняя плата формирует сигнал DACKN и устанавливает сигнал MASTER,

блокирующий выход КПДП на системную шину.

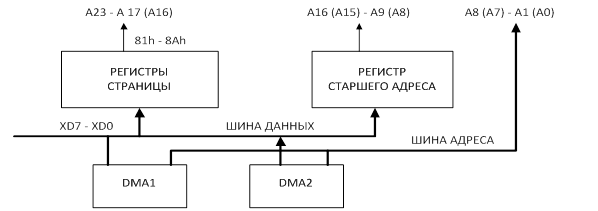

Рассмотрим

схему формирования адреса (рис. 3.13).

Рис. 3.13. Схема формирования адреса

Схема формирования адреса содержит внешние по отношению к DMA

регистры страницы и регистр старшего адреса. Регистры страницы - это байтовые

порты с адресами из диапазона 81h-8Ah, загружаемые заранее процессором по шине

XD7 – XD0 на этапе инициализации КПДП. Адресация регистров страницы каналов K0

– K7 показана в табл. 3.4.

Таблица 3.4

|

Канал

|

Адреса регистров страницы (h)

|

|

К0

|

87

|

|

К1

|

83

|

|

К2

|

81

|

|

К3

|

82

|

|

К5

|

88

|

|

К6

|

89

|

|

К7

|

8А

|

Необходимость использования внешнего регистра старшего адреса

связана с тем, что старшая часть адреса выводится из DMA по шине данных и

запоминается в этом регистре по сигналам DMA. Младшая часть адреса выводится

непосредственно по шине адреса DMA. На рис. 3.13 представлено, что в случае

использования одного из каналов K5 –K7, связанных с 16-битовыми передачами,

регистр страницы хранит адресные биты A23 –A17, регистр старшего адреса –

адресные биты A16 - A9, а по адресной шине выводятся адресные биты A8 –A1.

Адресный бит A0 в этом случае всегда равен 0, так как слова имеют четный адрес.

Байтовые передачи данных связаны с обычным распределением битов адреса, которые

(см. рис. 3.13) указаны в скобках.

Внутренняя шина XD7–XD0 подключена к системной шине SD7–SD0

через соответствующий приемопередатчик (это подключение на рис. 3.13 не

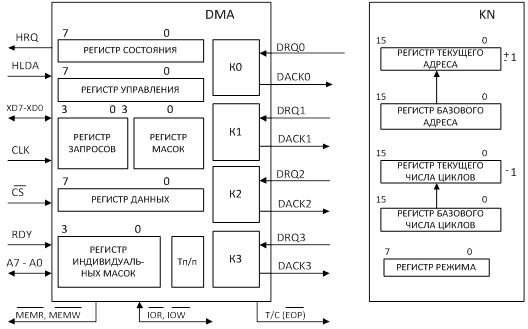

показано). Схема портов DMA изображена на рис. 3.14.

Рис. 3.14. Схема

портов DMA

Перечень адресов регистров DMA1 и DMA2 приведен в табл. 3.5.

Таблица

3.5

|

Режимы

W-запись

R-чтение

|

Число бит

|

Адреса

|

Назначение

регистров (портов)

|

|

|

DMA1

(h)

|

DMA2

(h)

|

|

|

|

W

|

8

|

08

|

0D

|

Регистр

управления (команд)

|

|

|

R

|

8

|

08

|

0D

|

Регистр

состояния

|

|

|

W

|

8

|

0B

|

D6

|

Регистр режима

|

|

|

W

|

4

|

0A

|

D4

|

Регистр

одиночны масок

|

|

|

W

|

4

|

0F

|

DE

|

Регистр масок

|

|

|

W

|

4

|

09

|

D2

|

Регистр

запросов

|

|

|

W

|

*

|

0E

|

DC

|

Сброс регистра

маски

|

|

|

W

|

*

|

0C

|

D8

|

Сброс триггера

первый/ последний (Тп/п)

|

|

|

R

|

8

|

0D

|

DA

|

Регистр данных

|

|

|

R/W

|

16

|

00

|

C0

|

Регистр

текущего адреса канала0/канала4

|

|

|

R/W

|

16

|

01

|

С2

|

Регистр

текущего числа циклов канала 0/канала 4

|

|

|

R/W

|

16

|

02

|

C4

|

Регистр

текущего адреса канала 1/канала 5

|

|

|

R/W

|

16

|

03

|

С6

|

Регистр

текущего числа циклов канала 1/канала 5

|

|

|

R/W

|

16

|

04

|

С8

|

Регистр

текущего адреса канала 2/канала 6

|

|

|

R/W

|

16

|

05

|

СА

|

Регистр

текущего числа циклов канала 2/канала 6

|

|

|

R/W

|

16

|

06

|

СС

|

Регистр

текущего адреса канала 3/канала 7

|

|

|

R/W

|

16

|

07

|

СЕ

|

Регистр

текущего числа циклов канала 3/канала 7

|

|

Примечание: * - порт

без передачи данных.

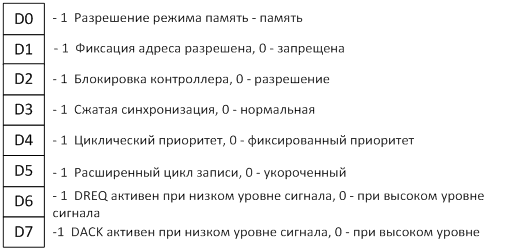

Регистр управления (команд) координирует работу DMA и

доступен по записи со стороны процессора. Формат регистра управления

представлен на рис. 3.15.

Биты D0 и D1 определяют режим память-память, когда данные передаются

из одной области оперативной памяти в другую область, причем этот обмен

осуществляется через регистр данных (порт 0Dh) каналами K0 иK1. В режиме

память-память в К0 задается адрес памяти (источник данных) и количество

передаваемых данных, а в К1 - адрес памяти (получателя данных). Сброс бита D1

регистра управления позволяет тиражировать один и тот же байт данных из одной

области памяти в различные ячейки другой области памяти.

Рис. 3.15. Формат

регистра управления (команд)

Сжатая синхронизация (D3=1) исключает некоторые такты в

работе DMA, если старшая часть адреса (А8-А15) не изменяется. Циклический

приоритет (D4=1) заключается в равноправном (последовательном) обслуживании

каналов DMA. Например, при D4=1 возможна следующая очередность приоритетов: К1

К0 К3 К2, К0 К3 К2 К1, К3 К2 К1 К0 и т.д. Фиксированный приоритет (приоритет

места) устанавливает степень приоритета в зависимости от номера канала, т.е.

канал К0 обладает наивысшим приоритетом, а канал К3 – низшим приоритетом.

При изменении старшей части адреса программируется

расширенный цикл записи (удлиняются сигналы  и и  ).Следует отметить, что КПДП формирует

пары сигналов: при чтении памяти ).Следует отметить, что КПДП формирует

пары сигналов: при чтении памяти  и и  и при записи в память и при записи в память  и и  , т.е.

в первом случае информация читается из ячейки оперативной памяти (сигналом , т.е.

в первом случае информация читается из ячейки оперативной памяти (сигналом  ), а потом записывается в регистр данных

контроллера периферийного устройства (сигналом ), а потом записывается в регистр данных

контроллера периферийного устройства (сигналом  ). Во

втором случае, наоборот, содержимое регистра данных контроллера периферийного

устройства читается по сигналу ). Во

втором случае, наоборот, содержимое регистра данных контроллера периферийного

устройства читается по сигналу  , а потом записывается

в память по сигналу , а потом записывается

в память по сигналу  . По умолчанию задается

удлиненный цикл записи и нормальная синхронизация. . По умолчанию задается

удлиненный цикл записи и нормальная синхронизация.

Биты D7 и D6 регистра управления определяют активный уровень

сигнала (0 или 1).

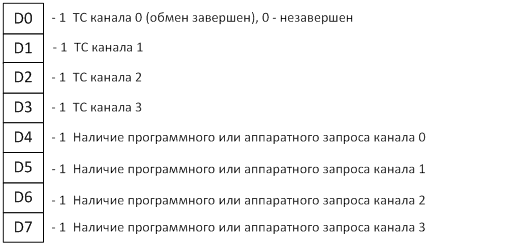

Содержимое регистра состояния доступно по чтению со стороны

процессора и имеет следующий формат (рис. 3.16).

Рис. 3.16. Формат

регистра состояния

Содержимое регистра текущего числа циклов (счетчика) канала N

(N= ) уменьшается после каждого цикла ПДП и,

как только оно станет равным FFFFh (обмен завершен), это состояние отмечается

установкой бита DN регистра состояния и на выходе DMA формируется сигнал T/C

(окончание счета), используемый в контроллере периферийного устройства для

формирования сигнала запроса прерывания. ) уменьшается после каждого цикла ПДП и,

как только оно станет равным FFFFh (обмен завершен), это состояние отмечается

установкой бита DN регистра состояния и на выходе DMA формируется сигнал T/C

(окончание счета), используемый в контроллере периферийного устройства для

формирования сигнала запроса прерывания.

В битах D4-D7 регистра состояния отмечается наличие

программного запроса в регистре запросов DMA или аппаратного запроса DRQN.

Программный запрос инициирует работу DMA так же, как и аппаратный запрос DRQN и

используется в прикладных программах, связанных с передачей массивов данных в

оперативную память.

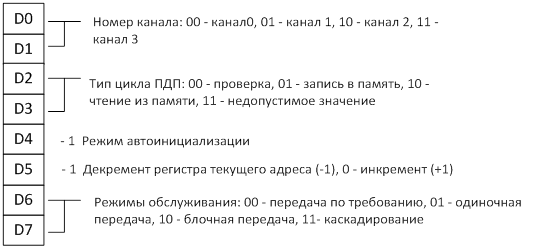

Каждому каналу соответствует 8-битовый регистр режима,

имеющий адрес 0Bh (D6h). Кроме того, в байте данных режима необходимо указать в

битах D1 и D0 номер канала DMA, для которого предназначен этот байт данных.

Формат регистра режима изображен на рис. 3.17.

Рис. 3.17. Формат регистра режима

Рассмотрим

режимы обслуживания DMA. Блочная (монопольная) передача выполняется непрерывно

до тех пор, пока содержимое регистра текущего числа циклов в KN не станет

равным FFFFh (обмен завершен). Передача по требованию осуществляется так же,

как и блочная, за исключением того, что она выполняется пока удерживается

сигнал DRQN. Снятие сигнала DRQN останавливает управление передачей данных,

которая возобновляется с той же точки при появлении сигнала DRQN. Наиболее

употребительным режимом является одиночная передача, состоящая в том, что после

передачи очередного байта DMA освобождает системную шину и начинает затем

запрос шины для управления передачей следующего байта. Этот процесс продолжается

до тех пор, пока содержимое регистра текущего числа циклов не станет равным

FFFFh (обмен завершен). Режим каскадирования, как уже отмечалось, используется

для увеличения числа каналов КПДП путем соединения нескольких DMA.

С помощью бита D5 программируется либо увеличение содержимого

регистра текущего адреса KN, либо его уменьшение.

Если бит D4=1 и сигнал T/C (EOP) равен 0 (обмен завершен), то

осуществляется автоматическая перезагрузка регистров базового адреса и базового

числа циклов соответственно в регистры текущего адреса и текущего числа циклов.

Биты D3 и D2 позволяют программировать тип цикла ПДП: запись

в память (01), при выполнении которой формируется сигнал  и и  ;

чтение из памяти (10), вырабатывающее сигналы ;

чтение из памяти (10), вырабатывающее сигналы  и и  . .

Цикл «проверка» (псевдопередача) заключается в том, что

выполняется цикл записи (чтения) с формированием адреса, но без передачи

данных.

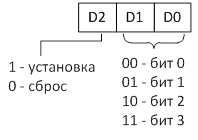

Регистру одиночных масок присвоен адрес 0Ah (D4h), см. табл.

3.9. По этому адресу направляется 3-битовая команда, в которой биты D1 иD0

указывают на номер бита в регистре одиночных масок, а бит D2 определяет

значение этого бита (1 или 0). Формат команды доступа к биту показан на рис.

3.18.

Рис. 3.18. Формат команды доступа к

биту

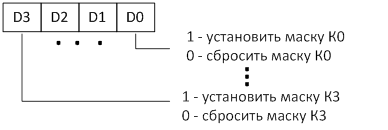

Установка программного запроса выполняется с помощью команды

(см. рис. 3.18.), посылаемой в 4-битовый регистр запросов по адресу 09h (DMA1)

или D2h (DMA2), причем бит D2=1 указывает на наличие запроса. Для осуществления

одновременной установки (сброса) битов регистра маски необходимо по адресу 0Fh

(DMA1) или DFh (DMA2) направить команду доступа к битам (D3-D0), имеющую

следующий формат (рис. 3.19).

Рис. 3.19. Формат команды доступа к

битам маски

По сигналу RESET (сброс) выполняется установка всех битов

регистра маски, которые блокируют все программные или аппаратные запросы DMA. С

помощью порта 0Eh (DMA1) или DCh (DMA2)(сброс регистра маски) можно разрешить

обработку запросов DMA.

В DMA применяется двунаправленная 8-битовая шина данных, по

которой происходит запись выводимых из процессора байтов данных в 16-битовые

регистры выбранного канала. Для управления занесением байта данных в младшую

часть (А7-А0) или старшую часть (А15-А8), например, регистра текущего адреса

используется триггер первый/последний (Тп/п), который при нулевом значении

разрешает запись байта данных в младшую часть регистра, а при единичном

значении – в старшую часть регистра. При инициализации DMA в начале программы

следует один раз сбросить триггер Тп/п, который затем автоматически

устанавливается (сбрасывается) при передаче каждого байта.

Регистр данных DMA предназначен для временного хранения байта

данных, передаваемого в режиме память-память. После завершения передачи байтов

данных, последний байт может быть считан и введен в процессор.

Каждый канал DMA содержит четыре 16-битовых регистра. Регистр

текущего адреса после передачи каждого байта( слова) автоматически уменьшается

или увеличивается на единицу. В циклах ПДП биты А 7-А 0 выводятся по шине

адреса DMA, биты А7-А0 выводятся по шине адреса DMA, а биты А8-А15 – по шине

данных.

Регистр текущего числа циклов (счетчик) задает количество

передаваемых байтов (слов) и уменьшается на 1 после каждого цикла ПДП. Если

содержимое этого регистра равно FFFFh, то это означает, что обмен данными

завершен. Поэтому начальное значение, заносимое в регистр текущего числа

циклов, должно быть уменьшено на 1.

Для реализации режима автоматизации в каждом канале имеется

регистр базового адреса и регистр базового числа циклов, которые загружаются

начальными значениями соответствующих текущих регистров и затем используются

для повтора передачи данных.

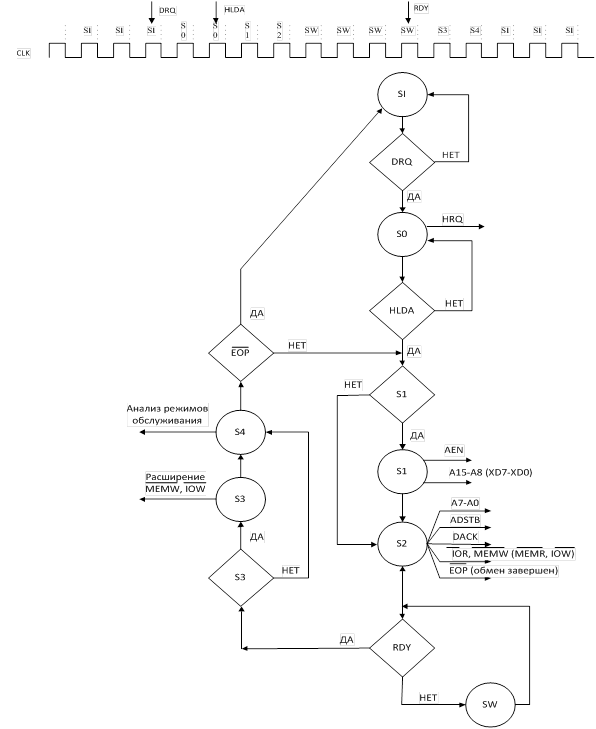

В работе КПДП можно выделить 2 режима: режим связи с

процессором (инициализации КПДП) и режим управления передачей данных между

оперативной памятью и периферийным устройством (блочной передачей в циклах

ПДП). В первом режиме процессор является задатчиком на системной шине, а КПДП –

исполнителем. Режим инициализации КПДП выполняется, если сигналы CS=DRQ=0, т.е.

отсутствует режим ПДП. Для доступа к портам DMA используются 4 младших бита

адреса А3-А0 (см. табл. 3.2), сигналы CS, IOR и IOW. Здесь следует иметь ввиду,

что на адресные выводы А 3-А 0 DMA2 подаются соответственно смещенные адресные

сигналы ХА4 –ХА1 (рис. 3.20).

Рис. 3.20. Схема подключения к DMA младших битов адреса

Процессор при инициализации КПДП выполняет следующую

последовательность действий.

1.

Программирует

регистр режима заданного канала DMA(операцию запись или чтение, тип передачи,

инкремент или декремент адреса).

2.

Вычисляет

24-битовый адрес памяти.

3.

Сбрасывает

триггер первый / последний (Тп/п).

4.

Выводит младший и

старший байты в регистр текущего адреса канала.

5.

Устанавливает

старшую часть адреса в требуемый регистр страницы.

6.

Направляет

младший и старший байты в регистр текущего числа циклов канала.

7.

Сбрасывает бит

маски выбранного канала DMA (открывает канал).

Во втором режиме (циклах ПДП) КПДП является задатчиком на

шине, а оперативная память – исполнителем. На рис. 3.21 представлена упрощенная

блок-схема циклов ПДП.

При выполнении режима ПДП DMA в соответствии с

синхросигналами CLK переходит условно или безусловно из одного состояния,

например, S0 в другое состояние S1, выполняя соответствующие функции. Состояние

SI является исходным (пассивным) состоянием DMA, при котором опрашиваются

сигналы запросов ПДП (DRQN). С поступлением активного сигнала DRQN DMA переходит

в состояние S0, формируя сигнал запроса шины (HRQ). После этого DMA ожидает

приход сигнала подтверждения шины (HLDA). Сигнал HLDA устанавливает КПДП

задатчиком на системной шине.

Рис. 3.21. Упрощенная

блок-схема циклов ПДП

Если старшая

часть адреса (А15-А8) не изменяется, то можно исключить программным способом

состояние S1 (сжатая синхронизация), связанное с выводом старшей части адреса.

С этой целью проверяется условие S1, указывающее на обход или переход к

состоянию S1. Обход состояния S1 осуществляется в том случае, если в регистре

управления DMA задана сжатая синхронизация. В состоянии S1 DMA вырабатывает

сигнал разрешения адреса AEN и выдает биты старшей части адреса А15-А8 по шине

данных XD7-XD0. После перехода в состояние S2 DMA реализует следующие действия:

1.

Выводит младшую

часть адреса (А7-А0) по шине адреса.

2.

Формирует сигнал

строб адреса (ADSTB) для фиксации битов А15-А8 во внешнем регистре.

3.

Вырабатывает

сигнал подтверждения ПДП (DACK) в контроллер периферийного устройства.

4.

Устанавливает

сигналы  и и  при

записи в память или при

записи в память или  и и  при

чтении памяти. при

чтении памяти.

5.

Формирует сигнал

EOP, если обмен завершен.

Для согласования с «медленной» памятью используется сигнал

готовности (RDY). Пассивный уровень сигнала RDY вызывает в DMA состояние

ожидания (SW). С появлением активного уровня сигнала RDY DMA анализирует

осведомительный сигнал S3 и если запрограммирована сжатая синхронизация, то

состояние S3 исключается. Для нормальной синхронизации состояние S3 выполняется

и формируются расширенные сигналы записи  и и  , учитывающие изменение старшей части

адреса. В состоянии S4 DMA выполняет анализ режимов обслуживания (одиночная передача,

блочная передача или это передача по требованию) и в зависимости от сигнала EOP

переходит в исходное состояние или на продолжение следующего цикла ПДП. , учитывающие изменение старшей части

адреса. В состоянии S4 DMA выполняет анализ режимов обслуживания (одиночная передача,

блочная передача или это передача по требованию) и в зависимости от сигнала EOP

переходит в исходное состояние или на продолжение следующего цикла ПДП.

Похожие материалы:

Прямое смешанное сообщение

Прядильщик (Выпуск №44 ЕТКС)

Пружинщик

Прямой маркетинг

Прямые зарубежные инвестиции. Мотивы осуществления ПЗИ. Концепция контроля - Проклин А.Н. Мировая экономика

Прямые материальные затраты на производство продукции

|