|

В.А. Авдеев, В.Ф. Гузик

Компьютеры: шины, контроллеры, периферийные устройства

Учебное пособие. Таганрог: ТРТУ, 2001. - 536 с.

3. Способы обмена данными

3.4. Многофункциональный контроллер ПДП

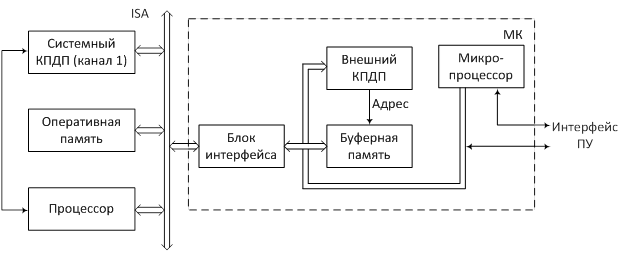

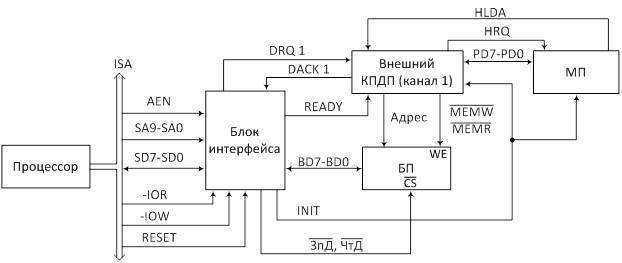

В качестве примера использования микросхемы КПДП (I8237) и координации ее работы в составе

системы рассмотрим обобщенную структурную схему многофункционального

контроллера (МК), представленную на рис. 3.22.

Программируемый МК предназначен для сопряжения процессора с

ПУ различных типов и содержит: буферную память (БП), необходимую для

согласования скоростей передачи данных между ПУ и процессором; внешний КПДП и

микропроцессор (МП), однокристальный микроконтроллер, имеющий специальное

программное обеспечение. Внешний КПДП участвует в управлении передачами данных

между: БП и оперативной памятью (ОП) в циклах ПДП (для выполнения этой

Рис.

3.22. Обобщенная структурная схема МК с ПДП

цели в системном КПДП используется канал 1, а во внешнем КПДП

– канал 0), БП и процессором (канал 1 внешнего КПДП), БП и МП (канал 2 внешнего

КПДП), БП и периферийным интерфейсом (канал 3 внешнего КПДП). Инициализацию

внешнего КПДП осуществляет МП, который задает в соответствующих каналах

начальный адрес БП, количество передаваемых байтов и нормальные режимы их

работы (без сжатой синхронизации). При рассмотрении МК основное внимание будет

уделяться организации взаимодействия процессора и МК (записи или чтения данных

из БП) и системного КПДП с МК в циклах ПДП.

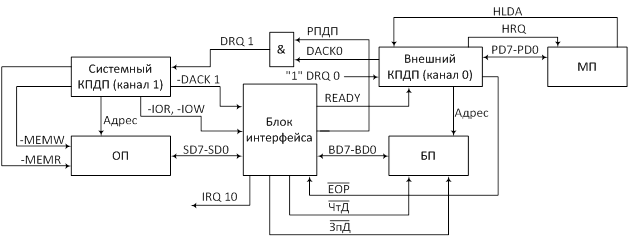

На рис. 3.23 изображена структурная схема передачи данных

между ОП и БП в циклах ПДП.

Рис.

3.23. Структурная схема передачи данных между ОП и БП

Рассмотрим, например, цикл режима чтения блока данных из ОП и

запись их в БП. Последовательность действий начинается с того, что МП

инициализирует канал 0 внешнего КПДП и открывает его (сбрасывает бит маски). На

вход активного канала 0 поступает запрос DRQ0 и внешний КПДП формирует сигнал запроса шины (HRQ), поступающий в МП. После установки

сигнала HLDA со стороны МП внешний КПДП получает

управление, направляет начальный адрес в БП, формирует сигнал подтверждения ПДП

(DACK 0) и переходит в состояние ожидания

до получения сигнала READY.

При наличии разрешения ПДП (РПДП), заранее установленного в

блоке интерфейса со стороны процессора, на вход системного КПДП поступает

запрос DRQ1. Системный КПДП захватывает

интерфейс, выводит адрес в ОП, осуществляет чтение содержимого выбранной ячейки

ОП по сигналу –MEMR,

устанавливает сигнал –DACK1,

разрешающий работу приемопередатчика и ДшУС в блоке интерфейса, схемы которых

будут представлены ниже. После этого системный КПДП формирует сигнал –IOW (запись в порт), по которому блоком

интерфейса вырабатываются: сигнал записи данных ( ) и

сигнал готовности (READY), запускающий

внешний КПДП на продолжение работы канала 0. Байт данных из ОП по шине SD7-SD0 поступает через открытый сигналом DACK1 приемопередатчик блока интерфейса на буферизованную

шину BD7-BD0 и записывается в ячейку БП, выбранную адресом внешнего

КПДП, по сигналу ) и

сигнал готовности (READY), запускающий

внешний КПДП на продолжение работы канала 0. Байт данных из ОП по шине SD7-SD0 поступает через открытый сигналом DACK1 приемопередатчик блока интерфейса на буферизованную

шину BD7-BD0 и записывается в ячейку БП, выбранную адресом внешнего

КПДП, по сигналу  блока интерфейса. С

поступлением сигнала READY

во внешний КПДП завершается его цикл работы, связанный с передачей одного байта

(увеличивается или уменьшается текущий адрес БП и уменьшается содержимое

счетчика байтов). Если внешний КПДП запрограммирован на выполнение блочного

режима работы, то осуществляется очередной цикл ПДП. блока интерфейса. С

поступлением сигнала READY

во внешний КПДП завершается его цикл работы, связанный с передачей одного байта

(увеличивается или уменьшается текущий адрес БП и уменьшается содержимое

счетчика байтов). Если внешний КПДП запрограммирован на выполнение блочного

режима работы, то осуществляется очередной цикл ПДП.

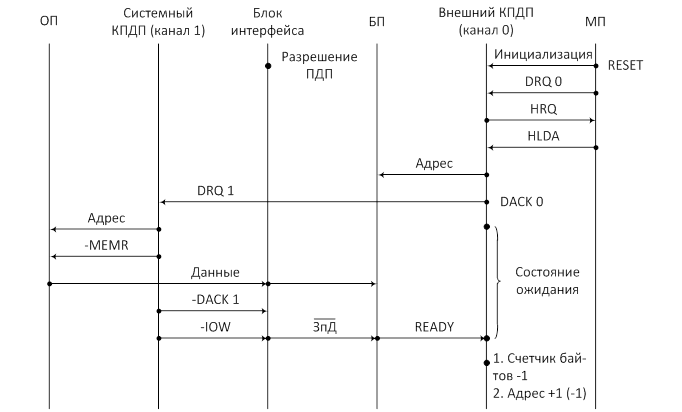

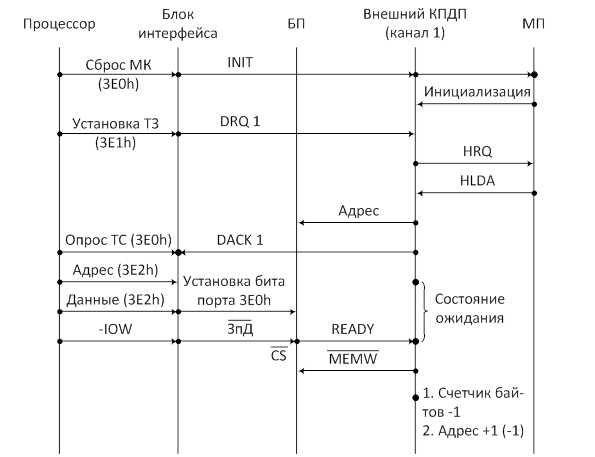

Описанная последовательность основных действий компонентов

системы (диаграмма режима чтения ОП в циклах ПДП) показана на рис. 3.24.

Рис.

3.24. Диаграмма чтение ОП в циклах ПДП

Аналогичным образом выполняется чтение блока данных из БП и

запись их в ОП за исключением того, что в этом случае по сигналу –DACK1 блоком интерфейса (ДшУС)

формируется сигнал чтения данных ( ), по которому

осуществляется выдача байта данных из БП по шине BD7-BD0 через блок

интерфейса (приемопередатчик) по шине SD7-SD0 в ОП. ), по которому

осуществляется выдача байта данных из БП по шине BD7-BD0 через блок

интерфейса (приемопередатчик) по шине SD7-SD0 в ОП.

Системный КПДП вначале вырабатывает сигнал –IOR (чтение порта), который разрешает передачу

данных из БП на шину ISA

(открывает в соответствующем направлении приемопередатчик блока интерфейса) и

формирует сигнал READY. Затем

системный КПДП устанавливает сигнал –MEMW, записывающий данные в выбранную ячейку ОП.

Упрощенная диаграмма режима записи данных в ОП представлена в

циклах ПДП на рис. 3.25.

Рис. 3.25. Упрощенная

диаграмма режима записи данных в ОП Рис. 3.25. Упрощенная

диаграмма режима записи данных в ОП

Циклы ПДП выполняются до тех пор, пока содержимое счетчика

байтов в канале 0 внешнего КПДП не станет равным FFFFh, при этом на его выходе формируется сигнал  (окончание счета), участвующий в

вырабатывании сигнала прерывания, например, IRQ N, сообщающему процессору о завершении передачи блока данных.

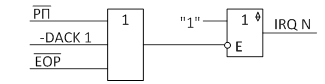

Для формирования сигнала IRQ N, кроме того, необходимы

сигналы разрешения прерывания ( (окончание счета), участвующий в

вырабатывании сигнала прерывания, например, IRQ N, сообщающему процессору о завершении передачи блока данных.

Для формирования сигнала IRQ N, кроме того, необходимы

сигналы разрешения прерывания ( ) и сигнал –DACK 1 (рис. 3.26). ) и сигнал –DACK 1 (рис. 3.26).

Рис. 3.26. Схема формирования сигнала

IRQ N

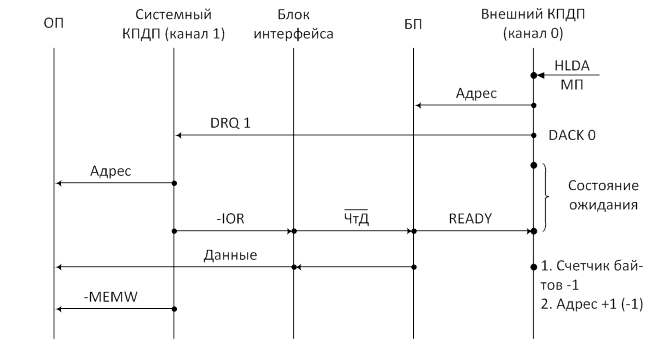

Передача данных между процессором и БП многофункционального

контроллера выполняется следующим образом. На рис. 3.27 показана структурная

схема сопряжения процессора и МК, осуществляющая передачу данных между

процессором и БП, управление работой которого выполняет внешний КПДП (канал 1).

Рис. 3.27. Структурная схема передачи

данных между процессором и БП

Взаимодействие процессора и МК начинается с доступа его к

порту (3E0h) сброса МК блока интерфейса, при этом внешний КПДП и МП

сигналом INIT приводятся в исходное состояние и микропроцессором

(МП) выполняется инициализация внешнего КПДП (канала 1) на прием данных в БП со

стороны процессора. Затем процессор устанавливает триггер запроса (порт 3E1h) в блоке интерфейса и на его выходе формируется сигнал DRQ 1 (запрос ПДП канала 1), запускающий

внешний КПДП на выполнение заданного режима. Внешний КПДП, получив сигнал DRQ 1, устанавливает сигнал HRQ (запрос шины) на соответствующий

вход МП. В свою очередь, МП направляет на внешний КПДП сигнал HLDA, передающий ему управление работой

БП. После этого канал 1 внешнего КПДП выполняет соответствующие такты

состояния, в результате чего устанавливается адрес ячейки БП и формируется

сигнал DACK 1, который поступает в блок

интерфейса и устанавливает соответствующий триггер регистра состояния (порта 3E0h). Адрес удерживается на адресных выходах внешнего КПДП,

который приостанавливает свою работу (состояние ожидания) до появления сигнала READY (готовности). Для упрощения (см.

рис. 3.27) адрес БП выбран 8-битным (А7-А0). При необходимости употребления

адреса А15-А0 следует использовать внешний регистр старшего адреса, который

загружается по шине данных внешнего КПДП битами А15-А8, а запись их выполняется

сигналом ADSTB.

Процессор путем опроса порта состояния (3E0h) определяет, что адрес ячейки БП установлен (имеется в

наличии сигнал -DACK 1) и можно

выводить информацию, которая может быть инструкциями для МП или данными. Число

выводимых байтов информации задается в счетчике байтов канала 1 внешнего КПДП.

Вывод байта данных с учетом порта данных (3E3h) осуществляется

по шине SD7-SD0 через блок интерфейса (приемопередатчик) по буферизованной

шине BD7-BD0 и сопровождается сигналом –IOW (запись данных). Блок интерфейса (ДшУС) формирует

сигнал  , который осуществляет разрешение работы

БП (выбор CS) и вырабатывает сигнал READY, запускающий внешний КПДП на

продолжение работы. Затем сигналом MEMW внешнего КПДП выполняется запись данных в БП. , который осуществляет разрешение работы

БП (выбор CS) и вырабатывает сигнал READY, запускающий внешний КПДП на

продолжение работы. Затем сигналом MEMW внешнего КПДП выполняется запись данных в БП.

Диаграмма передачи данных из процессора в БП изображена на

рис. 3.28.

Рис. 3.28. Диаграмма передачи данных из процессора в БП

Почти таким же образом выполняется ввод данных из БП в

процессор за исключением того, что после завершения опроса порта состояния (3E0h) процессор устанавливает адрес порта данных (3E3h) и сигнал –IOR,

по которому блок интерфейса (ДшУС) формирует сигнал чтения данных ( ). Сигнал ). Сигнал  осуществляет

вывод данных из БП на шину SD7-SD0 и участвует в формировании сигнала READY. В табл. 3.6 приведено описание

портов МК. осуществляет

вывод данных из БП на шину SD7-SD0 и участвует в формировании сигнала READY. В табл. 3.6 приведено описание

портов МК.

Таблица 3.6

|

Название порта

|

Адрес (h)

|

Доступ

|

Сигналы ДшУС

|

|

Сброс

|

3E0

|

W

|

|

|

Триггер запроса

|

3E1

|

W

|

|

|

Регистр состояния

|

3E0

|

R

|

|

|

Данные (Д)

|

3E3

|

W/R

|

/ /

|

|

Регистр разрешения (Р) ПДП и прерывания

|

3E2

|

W

|

|

|

Тип устройства (У)

|

3E2

|

R

|

|

Порт сброс

(3E0h) используется без передачи битов данных. При выводе из

процессора по адресу 3E0h на выходе ДшУС формируется сигнал  , который устанавливает внешний КПДП и МП

в исходное состояние и вызывает инициализацию канала 0 внешнего КПДП со стороны

МП. , который устанавливает внешний КПДП и МП

в исходное состояние и вызывает инициализацию канала 0 внешнего КПДП со стороны

МП.

После этого

процессор устанавливает триггер запроса (ТЗ), имеющий адрес 3E1h, с передачей бита данных по шине SD0 (BD0).

На выходе ТЗ формируется сигнал DRQ 1

(запрос ПДП канала 1), поступающий на соответствующий вход внешнего КПДП. В

результате взаимодействия внешнего КПДП с МП он получает доступ к БП и

устанавливает адрес его ячейки.

Процессор

опрашивает (читает в цикле) регистр состояния (3E0h), в котором

фиксируются сигналы DACK0-DACK3 внешнего КПДП, указывающие на

готовность БП к приему (передаче) данных. При выводе инструкций из процессора в

БП в регистре состояния должен быть установлен признак DACK1, указывающий процессору на готовность БП к приему

данных и направление передачи данных.

Запись

(чтение) данных в БП осуществляется с помощью порта данных (3E3h).

Порт типа

устройства (3E2h) представляет собой шинный формирователь (ШФ), на входы которого

подается с помощью перемычек код типа устройства.

В 2-битном

регистре разрешения (РР), имеющего адрес 3E2h (W), устанавливаются биты, разрешающие

режимы ПДП и прерывания.

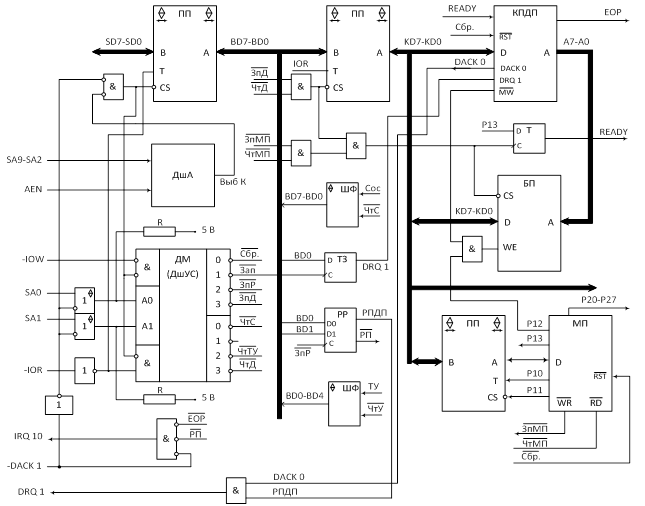

На рис. 3.29

представлена структурная схема МК, управление работой которого и передачами

данных выполняется с помощью перечисленных выше портов.

Рис.

3.29. Структурная схема МК

ДшУС

реализован на базе демультиплексора (ДМ) типа ИД4, особенностью работы которого

является то, что выходные сигналы  или или  формируются как в циклах ПДП при наличии

системного сигнала –DACK, так и в

режиме программного обмена процессора с БП, когда сигнал –DACK отсутствует. В обоих случаях на

адресных входах А1 и А0 присутствуют высокие уровни (код 11), позволяющие

установить сигнал формируются как в циклах ПДП при наличии

системного сигнала –DACK, так и в

режиме программного обмена процессора с БП, когда сигнал –DACK отсутствует. В обоих случаях на

адресных входах А1 и А0 присутствуют высокие уровни (код 11), позволяющие

установить сигнал  или или  ,

причем сигнал –IOR или –IOW в циклах ПДП формируется системным

КПДП, а в режиме программного обмена – процессором. ,

причем сигнал –IOR или –IOW в циклах ПДП формируется системным

КПДП, а в режиме программного обмена – процессором.

Похожие материалы:

Многообразие организационно-правового закрепления отношений собственности

Орлов А.И. Эконометрика: Многомерный статистический анализ

Многомерный статистический анализ

Множественность преступлений и ее виды

Множественность экземпляров коносамента - Кодекс торгового мореплавания

Мода на консультирование

|