|

В.А. Авдеев, В.Ф. Гузик

Компьютеры: шины, контроллеры, периферийные устройства

Учебное пособие. Таганрог: ТРТУ, 2001. - 536 с.

5. Локальные интерфейсы

5.3. Контроллер PCI 9060

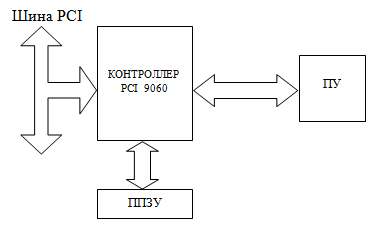

Для подключения ПУ к шине PCI фирмой PLX Technology

разработан однокристальный контроллер PCI9060 широкого назначения. На рис. 5.12

показана общая схема подключения необходимых компонентов к PCI 9060.

Рис. 5.12. Общая схема

подключения компонентов к PCI 9060

PCI 9060 выполняет режим мастера или исполнителя и

предназначен для сопряжения с ПУ, в качестве которых могут быть использованы

адаптеры (периферийные процессорные системы). Скорость передачи данных в режиме

мастер равна 132 Мбайт/с.

PCI 9060 поддерживает 32-, 16- или 8- битные раздельные или

мультиплексные локальные шины. К шине PCI контроллер подключается без

использования внешних формирователей и может устанавливать от нескольких

источников запрос на прерывание по шине PCI или по локальной шине, работающей

асинхронно по отношению к шине PCI, кроме того, к контроллеру через последовательный

интерфейс подключается ППЗУ для передачи информации о конфигурации и инициализации

микросхемы PCI 9060, выполненной по технологии КМОП и имеющей 208-выводной

пластиковый корпус типа QFP.

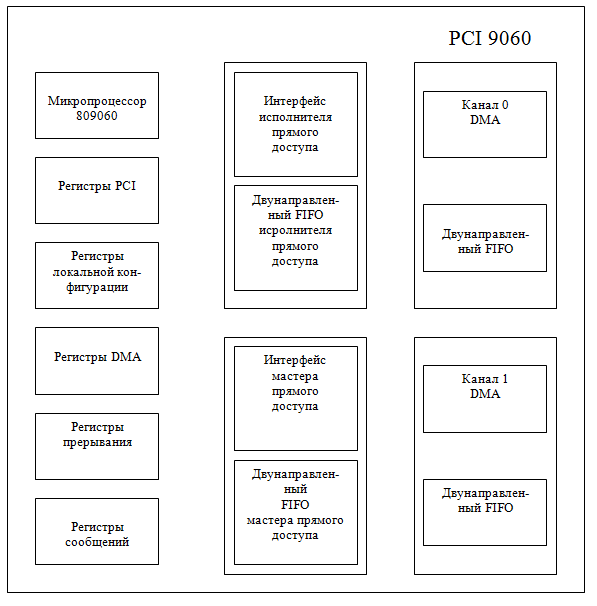

На рис. 5.13 изображена структурная схема контроллера PCI

9060.

Структурная схема содержит два независимых каналов DMA

(канал 0 и канал 1), предназначенных для взаимодействия с периферийной памятью.

PCI 9060 использует четыре двунаправленных FIFO для обеспечения пакетного

режима без затраты времени на ожидание очереди, причем возможно управление

передачей данных со стороны мастера прямого доступа и со стороны исполнителя

прямого доступа. Кроме того, в состав оборудования контроллера входят: восемь

32-битных регистров сообщений и два 32-битных регистра прерываний («дверных

звонков»), регистры локальной конфигурации, регистры PCI и DMA.

Рис. 5.13. Структурная схема контроллера PCI 9060

Доступ к перечисленным регистрам контроллера PCI 9060

возможен как со стороны мастера шины PCI, так и со стороны мастера локальной

шины путем использования внутренних или внешних схем декодирования адреса.

Первый регистр прерывания, предназначенный для управления формирования запроса

прерывания на локальной шине, программируется (устанавливается) мастером шины

PCI и сбрасывается мастером периферийной шины, а второй регистр прерывания,

наоборот, устанавливается мастером локальной шины для управления формированием

запроса прерывания на шине PCI и сбрасывается мастером шины PCI.

Контроллеры PCI 9060 выполняют для локальной шины три режима:

раздельные 32-битная шина адреса и 32-битная шина данных (режим (Х),

мультиплексная 32-битная шина адреса/данных (режим Iх) и мультиплексная

32-битная шина адреса/16-битная щина данных (режим Sx)). Эти режимы реализует

внутренний процессор 80960, координирующий работу всех блоков контроллера и

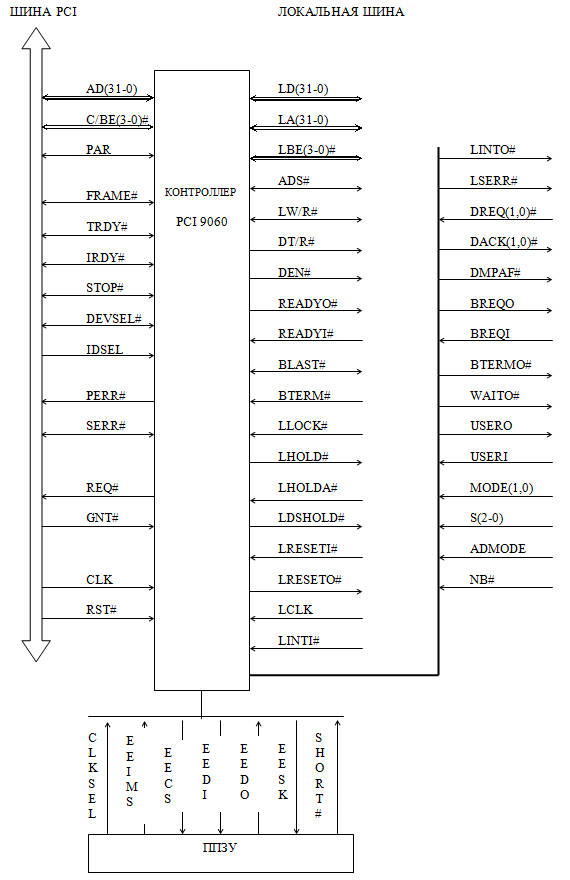

имеющий собственное специальное программное обеспечение. Схема сигналов

контроллера PCI 9060 представлена на рис. 5.14.

Рассмотрим функциональное назначение линий (сигналов)

контроллера PCI 9060, определяющих его работу со стороны периферийной шины.

LD(31-0) – локальная шина данных размерами 32-, 16- или 8-бит

в зависимости от текущей конфигурации шины.

LA(31-2) – локальная шина адреса, по которой передаются

старшие 30 бит адреса, наращиваемые во время пакетной передачи.

LBE(3-0)# - разрешение байта, которые кодируют 32-битную шину

LD следующим образом: BE3# соответствует наличию байта 3 на линиях LD(31-24),

BE2# - байта 2 на линиях LD(23-16), BE1# - байта 1 на линиях LD(15-8) и BE0# -

байта 0 на линиях LD(7-0). Если используется 16-битная шина, то BE3# определяет

старший байт данных на линиях LD(15-8), BE2# не используется, BE1# показывает

достоверность бита адреса LA1 и BE0# задает младший байт данных LD(7-0). Для 8-битной

шины BE3# и BE2# не используются, а BE1# и BE0# указывают соответственно на

достоверность битов адреса LA1 и LA0.

ADS# - строб адреса, определяющий действительный адрес в

начале каждого цикла.

LW/R# - сигнал операции записи (высокий уровень) или чтения

(низкий уровень).

DT/R# - сигнал передачи или приема (низкий уровень) данных.

DEN# - сигнал достоверности разрешения данных.

Рис. 5.14. Схема сигналов контроллера PCI 9060

READYO# - готовность вывода. Этот сигнал устанавливается PCI

9060 (исполнителем), чтобы сообщить мастеру локальной шины о том, что читаемые

данные достоверны или передача записываемых данных завершена.

READYI# - готовность ввода, формируется исполнителем

локальной шины и указывает PCI 9060 (мастеру) о том, что читаемые с шины данные

достоверны или передача записываемых данных завершена.

BLAST# - сигнал, устанавливаемый мастером локальной шины во

время последней передачи данных.

BTERM# - сигнал, прерывающий пакетную передачу и вызывающий

адресный цикл.

LLOCK# - сигнал, который указывает, что операция требует

завершения транзакции на шине.

LHOLD# - запрос локальной шины, устанавливаемый контроллером

PCI 9060.

LHOLDA# - подтверждение захвата сигнала локальной шины.

LDSHOLD# - запрос локальной шины исполнителем ПДП контроллера

PCI 9060, применяемый совместно с LHOLD.

LRESETI# - входной сигнал сброса, передаваемый по локальной

шине, которая очищает локальные регистры конфигурации PCI 9060 и вызывает

активный уровень сигнала LRESETO#.

LRESETO# - выходной сигнал сброса, выводимый контроллером PCI

9060 на локальную шину и удерживаемый в течение четырех периодов LCLK.

LCLK – сигналы синхронизации локальной шины.

LINTI# - входной сигнал прерывания, поступающий от

исполнителя локальной шины.

LINTO# - выходной сигнал прерывания контроллера PCI 9060.

LSERR# - сигнал системной ошибки.

DREQ(1,0)# - сигналы запросов ПДП соответственно к каналам 1

и 0.

DACL(1,0)# - сигналы подтверждения ПДП соответственно из

каналов 1 и 0.

DMPAF# - выходной программируемый сигнал мастера ПДП,

сообщающий о том, что FIFO почти полон.

BREQI – входной сигнал запрос шины. Если этот сигнал активен,

то PCI 9060 освобождает шину в течение DMA передачи.

BREQO – выходной сигнал запрос

шины, который формирует PCI 9060, требующий локальную шину.

BTERMO# - сигнал, сообщающий о том, что пакетная передача

завершается и начинается новый цикл.

WAITO# - выход, указывающий состояние программируемого

генератора ожидания.

USERO – универсальный выход пользователя, управляемый PCI

9060 через регистр конфигурации.

USERI – универсальный вход пользователя, состояние которого

отмечается в регистре конфигурации PCI 9060.

MODE(1,0) – сигналы режима шины, выбирающие режим

функционирования шины (табл. 5.3).

Таблица 5.3

|

Бит 1

|

Бит 0

|

Режим шины

|

|

0

|

0

|

C

|

|

0

|

1

|

J

|

|

1

|

0

|

S

|

|

1

|

1

|

Резерв

|

ADMODE – входной сигнал режима декодирования адреса,

определяющий использование S(2-0) для доступа к внутренним регистрам PCI 9060.

S(2-0) – входные сигналы выбора адресса. Если ADMODE имеет

высокий уровень, то внутренние регистры PCI 9060 выбраны при совпадении S(2-0)

и A(31-29). В том случае, если ADMODE приобретает низкий уровень, то внутренние

регистры выделяются при низком уровне S0.

NB# - сигнал запрещения инициализации со стороны локальной

шины.

Следующая группа сигналов связана с подключением ППЗУ к

контроллеру PCI 9060.

CLKSEL – сигнал выбора внешнего или внутреннего регистра

синхросигнала. Если CLKSEL имеет низкий уровень, то для тактирования ППЗУ

используется вывод EEIMS, к которому подключается внешний источник

синхросигналов, в противном случае употребляются внутренние тактовые сигналы.

EEIMS – вывод для подключения внешних тактовых сигналов.

EECS – выбор кристалла ППЗУ.

EEDI – записываемые данные в ППЗУ.

EEDO – читаемые данные из ППЗУ.

EESK – CLK ППЗУ.

SHORT# - сигнал короткой загрузки. При активном сигнале SHORT#

только содержимое первых пяти 32-битных ячеек ППЗУ будут загружены в контроллер

PCI 9060.

Регистры конфигурации PCI 9060 программируются на этапе

инициализации со стороны ППЗУ или локального процессора. Во время инициализации

с помощью ППЗУ контроллер PCI 9060 не отвечает на запросы шины PCI, удерживает

READYO# в пассивном состоянии и на его вход NB# подан сигнал запрещения

инициализации со стороны локальной шины. Различают короткую или полную загрузку

регистров конфигурации PCI9060 содержимым ППЗУ. Полная или короткая загрузка

регистров конфигурации выполняется после сброса контроллера PCI9060 и при

наличии на входе SHORT# соответственно высокого или низкого уровня напряжения.

Для режима короткой загрузки в табл. 5.4 приведено описание информации ППЗУ.

Таблица 5.4

|

Смещение в ППЗУ

|

Значение

|

Описание

|

|

0

|

9060

|

Идентификатор устройства

|

|

2

|

10B5

|

Идентификатор

производителя

|

|

4

|

0680

|

Код класса устройства

|

|

6

|

0002

|

Номер версии

|

|

8

|

0000

|

Максимальное время

ожидания

|

|

A

|

0100

|

Вывод прерывания

|

|

C

|

****

|

Старшее слово почтового

ящика 0

|

|

E

|

****

|

Младшее слово почтового

ящика 0

|

|

10

|

****

|

Старшее слово почтового

ящика 1

|

|

12

|

****

|

Младшее слово почтового

ящика 1

|

Примечание: **** - значение не определено.

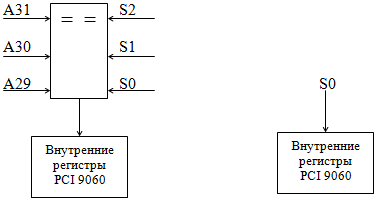

Доступ к внутренним регистрам PCI 9060 со стороны локальной

шины выполняется следующим образом. Если ADMOD=1 и S2=S1=S0=1, то в результате

32-битный адрес 111***…* относится к внутреннему адресному пространству PCI9060

и является начальным адресом для контроллера (Е0000000h).

На рис. 5.15 представлено два

способа доступа к внутреннему адресному пространству PCI9060.

Рис.

5.15. Два способа доступа к внутреннему адресному пространству PCI 9060

Через контроллер PCI9060 может быть выполнена пакетная

передача данных из процессора шины PCI в устройство, подключенное к локальной

шине. Кроме того, осуществляется и обратная пакетная передача данных из

процессора локальной шины в устройства шины PCI. Этими двунаправленными

передачами управляют регистры конфигурации, реализующие доступы к адресным

пространствам шины PCI и локальной шины.

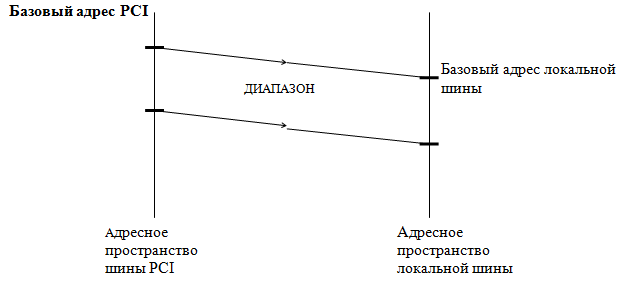

В режиме прямого доступа из локальной шины к шине

PCI для конфигурации этого режима применяются следующие регистры:

-

регистр

диапазона;

-

регистр

локального базового адреса памяти;

-

регистр

локального базового адреса ввода/вывода;

-

регистр адреса конфигурации

PCI:

-

регистр базового

адреса PCI.

Регистр диапазона задает биты локального адреса,

используемого для обращения к шине PCI со стороны локальной шины. Для доступа к

адресным пространствам памяти или ввода/вывода PCI процессора локальной шины

соответственно применяются регистры локального базового адреса памяти или

ввода/вывода.

В этом режиме употребляется FIFO, в котором 32 байта

используются для записи и 16 байтов для чтения, что позволяет выполнять

пакетные передачи и функционировать независимо от шины PCI. В режиме записи

PCI9060 устанавливает READYO# и принимает данные до тех пор, пока не заполнится

очередь, после чего контроллер сбрасывает READYO# до появления в очереди. Если

выполняется режим чтения, то PCI9060 удерживает READYO# при приеме 32-битных

данных из шины PCI. Цикл чтения завершается, если установлен BLAST#.

Аналогичным образом PCI9060 поддерживает режим прямого

доступа к адресному пространству памяти или ввода/вывода локальной шины со

стороны шины PCI. Для определения места в этих адресных пространствах

используются регистры базовых адресов памяти или ввода/вывода. Кроме того,

применяется регистр отображения, который определяет способ трансляции адреса

PCI в адрес локальной шины.

Канал передачи данных «шина PCI – локальная шина» содержит

FIFO, в котором 8 байтов используются для записи данных со стороны шины PCI и 8

байтов для чтения данных на локальную шину. Некоторые устройства, подключаемые

к локальной шине, используют дополнительные ПЗУ. Для того, чтобы управлять

содержимым адреса и размером расширения ПЗУ, со стороны шины PCI в PCI9060

предусмотрены: регистры диапазона ПЗУ расширения, регистр базового адреса ПЗУ

расширения и регистр характеристики локальной шины, инициализация которых

выполняется со стороны локальной шины.

Мастер шины PCI инициализирует в этом случае только регистр

базового адреса PCI для ПЗУ. Общая схема доступа к локальной шине со стороны

шины PCI показана на рис. 5.16.

Рис

5.16. Общая схема доступа шины PCI к локальной шине

Похожие материалы:

Контроллер ISA/ИРПР

Контролируемые сделки - ст.105.14 НК РФ

Контролер-приемщик фарфоровых, фаянсовых и керамических изделий

Контроллер НГМД

Контроллер комбинированного типа - Авдеев В.А. и др., 2001

Контроллер программного обмена

|