|

В.А. Авдеев, В.Ф. Гузик

Компьютеры: шины, контроллеры, периферийные устройства

Учебное пособие. Таганрог: ТРТУ, 2001. - 536 с.

6. Периферийные интерфейсы

6.12. Контроллер ISA/ИРПР

Рассмотрим

принцип построения контроллера ISA/ИРПР,

особенностью которого является то, что в качестве ДшУС используется ПЗУ и

предусматривается возможность подключения одного из нескольких ПУ, каждое из

которых может быть источником и приемником информации, источником или

приемником. Основное внимание здесь будет уделено вопросам синхронизации

двунаправленной передачи данных между процессором и ПУ через контроллер ISA/ИРПР. Связь ПУ с контроллером

выполняется с помощью интерфейса радиального параллельного (ИРПР). Контроллер

осуществляет режим программного обмена данными через прерывание или опрос флага

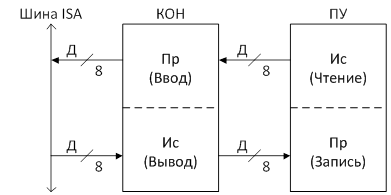

готовности. Общая схема связи ПУ, контроллера (КОН) и шины ISA показана на рис. 6.30.

Рис. 6.30. Общая схема связи ПУ, КОН и шины ISA

Контроллер содержит две основные части: приемник (Пр) и

источник (Ис). Приемник выполняет чтение данных из ВУ и ввод данных в

процессор, а источник – вывод данных из процессора и запись их в приемник ВУ.

Из

схемы видно, что источник (приемник) может быть как в контроллере, так и в ВУ.

Местонахождение приемника (источника) определяется режимом ввода или вывода. Как

уже отмечалось, ПУ подключается к контроллеру через интерфейс ИРПР.

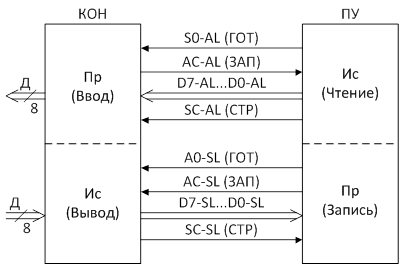

Интерфейс

ИРПР имеет следующие основные сигналы:

SC-AL и SC-SL – стробы источника при вводе и

выводе соответственно;

AC-AL и AC-SL – запрос приемника при вводе и

выводе соответственно;

A0-AL и A0-SL – готовность приемника при вводе и

выводе соответственно;

D7-AL…D0-AL – данные ввода;

D7-SL…D0-SL – данные вывода.

В

обозначениях сигналов буква А указывает на режим ввода сигнала, а буква L – на активный низкий уровень, буква S – на режим вывода. С учетом

обозначений сигналов схема связи ПУ и контроллера имеет вид, представленный на

рис. 6.31.

Рис. 6.31. Схема связи ПУ и КОН

Принцип

действия ИРПР прост: при наличии сигнала готовности Пр устанавливает сигнал запроса,

а Ис отвечает передачей данных (Д) и с некоторой задержкой сигналом строб

записи.

Контроллер содержит

четыре адресуемых регистра, с помощью которых процессор обменивается данными с

ПУ. Эти регистры имеют следующие обозначения:

-

2-битный регистр

управления/состояния ввода (РУ/С Вв);

-

8-битный регистр

данных ввода (РД Вв);

-

2-битный регистр

управления/состояния вывода (РУ/С Выв);

-

8-битный регистр

данных вывода (РД Выв).

С целью упрощения рисунков РУ/С взяты 2-битными.

Выбор соответствующего регистра в контроллере

определяется индексом (последней 16-ричной цифрой адреса).

В табл. 6.9 представлены индексы и

тип доступа соответствующих портов.

Таблица 6.9

|

Порт

|

Индекс (h)

|

Доступ

|

Сигналы ДшУС

|

|

РД Вв

|

0

|

R

|

IN0

|

|

РД Выв

|

1

|

W

|

OUT1

|

|

РУ/С Вв

|

2

|

W/R

|

OUT2/IN2

|

|

РУ/С Выв

|

3

|

W/R

|

OUT3/IN3

|

Примечание: IN - ввод, OUT – вывод.

Полный адрес порта ПУ, например РД Вв, равен 220h. К

контроллеру может быть подключено одно из трех различных ПУ, базовые адреса

которых 220h, 230h и 240h. Выбор заданного ПУ осуществляется с помощью

перемычек и наборного поля, находящихся в ДшА, который будет рассмотрен ниже.

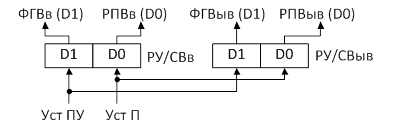

Форматы РУ/С Вв и РУ/С Выв представлены на рис. 6.32.

Рис.

6.32. Форматы РУ/С Вв и РУ/С Выв

Бит D1

РУ/С Вв (Выв) устанавливается (Уст) ПУ и на выходе триггера формируется сигнал

флаг готовности (ФГ) Вв (Выв), а бит D0 – процессором (П) и на выходе триггера формируется сигнал разрешения

прерывания (РП) Вв (Выв). Если выполняется вывод данных, то сброс ФГ Выв осуществляется

при записи данных в РД Выв, и наоборот, если производится ввод данных, то сброс

ФГ Вв выполняется при чтении данных из РД Вв.

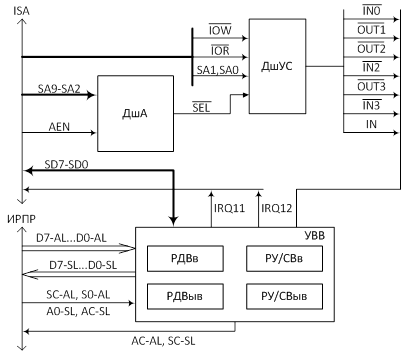

Структурная схема контроллера изображена на рис. 6.33.

Рис.

6.33. Структурная схема контроллера ISA/ИРПР

Дешифратор ДшА предназначен для дешифрирования адреса ПУ,

подключенного к контроллеру. ДшА принимает старшую часть адреса и формирует на

выходе SEL (выбор ПУ). Младшие биты адреса SA1 и SA0 используются для выбора одного из четырех регистров

(портов). ДшУС вырабатывает следующие сигналы в соответствии с табл. 6.9:

-

чтение РД Вв (IN0);

-

запись в РД Выв (OUT1);

-

запись в РУ/С Вв (OUT2);

-

чтение РУ/С Вв (IN2);

-

запись в РУ/С Выв (OUT3);

-

чтение РУ/С Выв (IN3);

-

общее чтение (IN).

Сигнал IN формируется, если

вырабатывается IN0, IN2 или IN3. Устройство ввода-вывода (УВВ) содержит четыре адресуемых

регистра, с помощью которых процессор обменивается данными с ПУ.

Двоичный эквивалент старшей части адреса показан на рис.

6.34, где символом “*” обозначены изменяемые биты базовых адресов (220h, 230h и 240h).

|

AEN

|

A9

|

A8

|

A7

|

A6

|

A5

|

A4

|

A3

|

A2

|

|

0

|

1

|

0

|

0

|

*

|

*

|

*

|

0

|

0

|

Рис. 6.34. Двоичный эквивалент

старшей части адреса

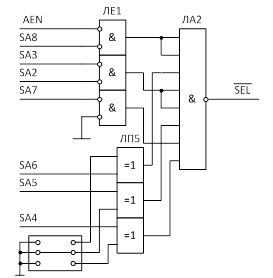

Схема ДшА

представлена на рис. 6.35 и позволяет с помощью перемычек задать базовый адрес

одного из трех ПУ.

Рис. 6.35. Схема ДшА

Схема ДшА,

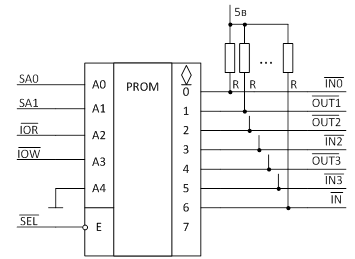

изображенная на рис. 6.35, настроена на базовый адрес 230h. На рис. 6.36 показана схема ДшУС,

реализованная на базе ППЗУ емкостью 32´8.

Рис.

6.36. Схема ДшУС

Схема ДшУС

функционирует в соответствии с табл. 6.10.

Таблица 6.10

|

Входы PROM

|

Выходы PROM

|

Операция

|

|

-E

|

A4

|

A3

|

A2

|

A1

|

A0

|

7

|

6

|

5

|

4

|

3

|

2

|

1

|

0

|

|

0

|

0

|

1

|

0

|

0

|

0

|

1

|

0

|

1

|

1

|

1

|

1

|

1

|

0

|

IN0

|

|

0

|

0

|

0

|

1

|

0

|

1

|

1

|

1

|

1

|

1

|

1

|

1

|

0

|

1

|

OUT1

|

|

0

|

0

|

0

|

1

|

1

|

0

|

1

|

1

|

1

|

1

|

1

|

0

|

1

|

1

|

OUT2

|

|

0

|

0

|

1

|

0

|

1

|

0

|

1

|

0

|

1

|

1

|

0

|

1

|

1

|

1

|

IN2

|

|

0

|

0

|

0

|

1

|

1

|

1

|

1

|

1

|

1

|

0

|

1

|

1

|

1

|

1

|

OUT3

|

|

0

|

0

|

1

|

0

|

1

|

1

|

1

|

0

|

0

|

1

|

1

|

1

|

1

|

1

|

IN3

|

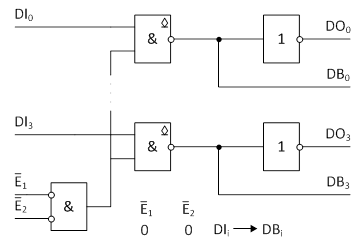

При

построении УВВ используется в качестве приемопередатчика микросхема 559ИП3, имеющая

4-битовые входы (DI), 4-битовые

выходы (DO) и 4-битовые инверсные

буферизированные входы/выходы (DB).

Микросхема 559ИП3 обладает следующими параметрами: для DB входной ток низкого уровня 2 мА и выходной ток низкого

уровня 70 мА; для DO выходной ток

низкого уровня 16 мА; время задержки tз. ср£35 нс. На рис. 6.37 показана принципиальная схема микросхемы 559ИП3 без

изображения номеров выводов.

Рис.

6.37. Принципиальная схема 559ИП3

Входы/выходы

DB обычно подключаются к

соответствующим линиям шины данных системного интерфейса, входы DI – к выходам регистра РВв, а выходы DO – ко входам регистра РВыв. Для

байтовой передачи данных необходимо использовать две микросхемы 559ИП3. На рис.

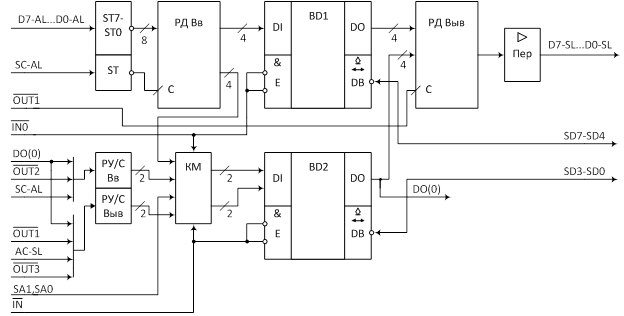

6.38 представлена структурная схема УВВ.

Рис.

6.38. Структурная схема УВВ

Установка

(сброс) триггеров РУ/С Вв и РУ/С Выв рассматривается отдельно в схеме управления

вводом/выводом.

Структурная

схема содержит два приемопередатчика BD1 и BD2 (две микросхемы 559ИП3). Старшие

биты D7-D4 РД Вв подключены ко входу DI BD1 и передаются на линии SD7-SD4 шины ISA по сигналу ДшУС IN0 (чтение данных РД Вв). Младшие биты

D3-D0 РД Вв поступают на входы комбинированного мультиплексора

(КМ), к которому присоединены также выходы регистров РУ/С Вв и РУ/С Выв.

Управление коммутацией входов и выходов КМ выполняют сигналы SA1, SA0, IN0 и IN. Кроме того, входы DI подключаются ко входам/выходам DB в приемопередатчике BD2 сигналом общего чтения IN, так как через BD2 в различные моменты времени

вводится в процессор содержимое РУ/С Вв, РУ/С Выв или младшие биты РД Вв. Из ПУ

данные передаются по линиям D7-AL…D0-AL через триггеры

Шмитта (ST7-ST0) на входы РД Вв и записываются в него сигналом строб записи

(SC-AL) ИРПР. Триггеры Шмитта имеют разные пороги включения и

выключения и повышают помехоустойчивость схемы. При выводе данных из процессора

они передаются по следующей схеме: SD7-SD0 ® DB (BD) ® DO (BD) ® ® РД Выв. Запись данных в РД Выв

осуществляется сигналом OUT1, сформированным

на соответствующем выходе ДшУС. С выходов РД Выв его содержимое передается с

помощью передатчиков (Пер) по линиям D7-SL…D0-SL ИРПР в ПУ.

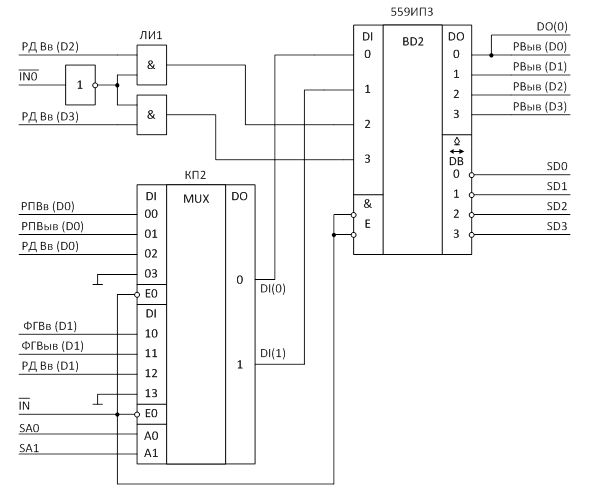

Схема КМ изображена на рис. 6.39.

Рис. 6.39. Схема КМ

При чтении содержимого РД Вв по сигналу ДшУС IN0 биты D2 и D3

через элементы И, а биты D1 и D0 через КМ поступают на входы DI микросхемы 559ИП3 (BD2). Управление коммутацией входов и

выходов КП2 выполняют адресные биты SA1 и SA0 (00) и сигнал общего чтения IN, комбинация которых в данном случае

соответствует сигналу IN0.

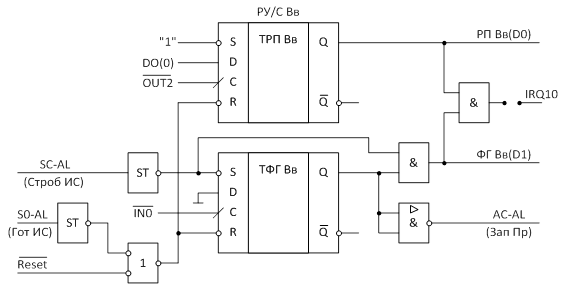

Функциональная схема управления вводом, построенная на базе

РУ/С Вв, представлена на рис. 6.40.

Рис.

6.40. Функциональная схема управления вводом

Триггер разрешения прерывания (ТРП) устанавливается со

стороны процессора с передачей бита данных по линии DO(0), где DO

обозначает выход BD2, а (0) –

соответствующий его вывод (см. рис. 6.39). Запись этого бита данных выполняется

сигналом OUT2, который формируется на соответствующем

выходе ДшУС (см. табл. 6.9).

Ввод данных из ПУ в процессор осуществляется по принципу

запрос-ответ с помощью сигналов AC-AL (запрос приемника) и SC-AL (строб источника). В исходном состоянии сигнал SC-AL имеет пассивный высокий уровень сигнала и поэтому триггер

ТФГ находится в единичном состоянии. Контроллер, являющийся приемником,

устанавливает AC-AL (Зап Пр) низким активным уровнем, в ответ на который ПУ

(источник информации) выдает байт данных на линии D7-AL…D0-AL и с задержкой устанавливает SC-AL (строб записи).

Строб SC-AL записывает байт данных в РД Вв (см. рис. 6.38) и

одновременно формируется сигнал ФГ Вв (D1) (см. рис. 6.40). Затем процессор путем опроса флага

готовности (чтения триггера ТФГ Вв) или в режиме прерывания (установлены триггеры

ТРП, ТФГ Вв и перемычка) IRQ10

осуществляет чтение содержимого РД Вв по сигналу ДшУС IN0. Этим же сигналом IN0 производится сброс триггера ТФГ Вв (снимается AC-AL и IRQ10 (в режиме прерывания)). В ответ на

сброс AC-AL ПУ снимает сигнал SC-AL, в результате чего триггер ТФГ Вв

устанавливается в единичное состояние и на его выходе вновь формируется AC-AL (Зап Пр).

В случае неготовности ПУ (источника информации) сигнал SC-AL имеет высокий пассивный уровень, триггер ТФГ находится в

нулевом состоянии и сигнал AC-AL на выходе триггера ТФГ Вв не

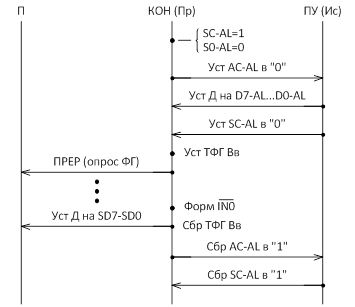

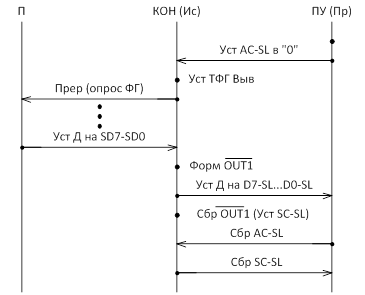

вырабатывается. Рассмотренная последовательность действий процессора (П),

контроллера (КОН) и ПУ при вводе данных показана на рис. 6.41.

Рис.

6.41. Последовательность действий П, КОН (Пр) и ПУ (Ис) при вводе данных

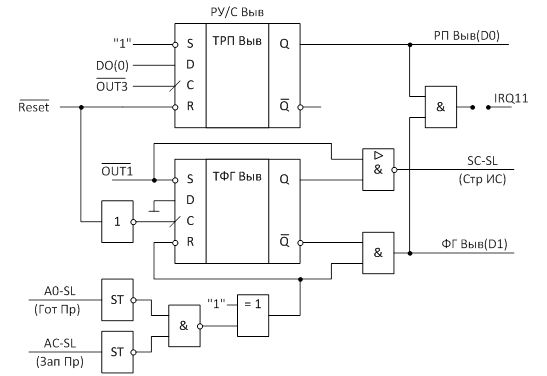

На рис. 6.42 изображена функциональная схема управления

выводом.

Вывод данных производится также по принципу запрос-ответ с

помощью сигналов AC-SL (Зап Пр) и SC-SL (Стр Ис). В

этом режиме КОН является источником (Ис) информации, а ПУ – приемником (Пр). В

исходном состоянии сигнал SC-SL (Стр Ис), формируемый КОН, имеет

высокий пассивный уровень, так как триггер ТФГ Выв находится в нулевом

состоянии. При необходимости приема данных ПУ (Пр) устанавливает сигналы AC-SL (Зап Пр) и A0-SL (Гот Пр) активными низкими уровнями.

Триггер ТФГ Выв сохраняет нулевое состояние и поэтому на выходе элемента И формируется

сигнал ФГ Выв (D1) высокого

активного уровня.

Рис.

6.42. Функциональная схема управления выводом

Процессор в

режиме прерывания (установлен триггер разрешения прерывания ТРП Выв) или по

опросу флага готовности (чтения значения ФГ Выв (D1)) выполняет запись данных в РД Выв по сигналу OUT1, формируемому ДшУС. Этим же

сигналом устанавливается триггер ТФГ Выв. При этом после снятия сигнала OUT1 формируется сигнал SC-SL (Стр Ис) низкого активного уровня и сбрасывается сигнал IRQ11 (в режиме прерывания). Как только

данные записаны в РД Выв, то они появляются на шине D7-SL…D0-SL интерфейса ИРПР. ПУ, получив сигнал SC-SL (Стр Ис), записывает

данные и сбрасывает AC-SL (Зап Пр). В ответ на сброс AC-SL контроллер снимает SC-SL. После завершения цикла обработки

байта данных ПУ устанавливает вновь сигнал AC-SL (Зап Пр), если

сброшен сигнал SC-SL (SC-SL имеет высокий

уровень). Последовательность действий при выводе данных П, КОН (Ис) и ПУ (Пр)

показана на рис. 6.43.

Рис.

6.43. Последовательность действий при выводе данных

П, КОН (Ис) и ПУ (Пр)

Похожие материалы:

Контролируемые сделки

Контролер-приемщик фарфоровых, фаянсовых и керамических изделий (Часть №1 выпуска №45 ЕТКС )

Контролер-приемщик вооружения

Контроллер PCI 9060

Контроллер НГМД - Авдеев В.А. и др., 2001

Контроллер комбинированного типа

|