|

В.А. Авдеев, В.Ф. Гузик

Компьютеры: шины, контроллеры, периферийные устройства

Учебное пособие. Таганрог: ТРТУ, 2001. - 536 с.

5. Локальные интерфейсы

5.2. Локальная шина PCI

Шина PCI

предназначена для работы с напряжением питания 5V или 3.3V и может быть использована

в серверах, настольных ПК, ноутбуках и лаптопах. Платы с разным питанием имеют

специальные ключи в некоторых местах контактов, кроме того, особенностью шины

PCI является то, что она не привязана к конкретному типу компьютера и

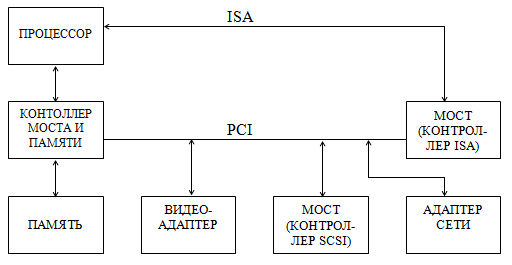

разработана с учетом на применение в новых системах. На рис. 5.1 представлена

возможная конфигурация компонентов, подключенных к шине PCI.

Рис. 5.1. Схема подключения

компонентов к шине PCI

Для шины PCI

определены два типа устройства: инициатор (мастер, задатчик) и целевое (исполнитель).

Инициатор устанавливает адрес (данные при записи), команду и формирует необходимые

интерфейсные сигналы целевому устройству. Причем адрес и данные передаются по

мультиплексной шине AD(31-0) или AD(63-0). Дальше (с целью упрощения материала)

основное внимание уделяется обязательным сигналам шины PCI, т.е.

рассматривается 32-битный вариант.

Рассмотрим назначение основных сигналов шины PCI. Символ #,

стоящий после названия сигнала шины PCI, указывает на то, что активным уровнем

этого сигнала является низкий уровень (логический 0). Кроме того, обозначение,

например (31-0), определяет группу линий (сигналов) с номерами от 31 до 0, t/s-

двунаправленный сигнал ввода-вывода с тремя состояниями, s/t/s – активный по

низкому уровню активный сигнал с тремя состояниями, in – стандартный сигнал

ввода, out – стандартный активный формирователь, o/d – открытый сток для

объединения сигналов (ИЛИ).

AD(31-0) t/s – мультиплексированная шина адреса/данных.

Шинное событие (транзакция) состоит из одной фазы адреса и одной или нескольких

следующих фаз данных.

C/BE(3-0)# t/s – мультиплексированная шина команды/разрешения

байтов. Во время фазы адреса выполняется передача команды (чтение или запись

ввода/вывода, чтение или запись в память и т.д.), а во время фазы данных –

битов, указывающих на значимые (разрешенные) байты на шине AD, например,

C/BE(3)# определяет байт 3 (AD31-AD24), C/BE(0)# - байт 0 (AD7-AD0).

PAR t/s – четный паритет сигналов AD(31-0) и C/BE(3-0)# для

всех агентов шины PCI.

Линии AD(31-0), C/BE(3-0)# и PAR относятся к линиям адреса и

данных. Следующую группу линий соответствующих сигналов составляют линии

сигналов управления интерфейсом.

FRAME# t/s – цикл кадра. Этот сигнал устанавливается

инициатором и указывает на начало транзакции шины , снятие сигнала означает

заключительную (финальную) фазу данных.

IRDY# s/t/s – готовность инициатора. Мастер формирует этот

сигнал, если способен передать или принять данные. Сигнал IRDY# употребляется

совместно с сигналом TRDY#. Фаза данных выполняется при наличии активных

(низких) уровней сигналов IRDY# и TRDY#. Если хотя бы один из этих сигналов

имеет пассивный (высокий) уровень, в работе инициатора вставляются такты ожидания.

TRDY# s/t/s – готовность цели показывает возможность

выбранного устройства закончить текущую фазу данных. При чтении TRDY# указывает

на достоверность передаваемых данных, а при записи – на готовность цели принять

данные.

STOP# s/t/s – стоп. Сигнал цели сообщает мастеру о приостановке текущего события.

LOCK# s/t/s – блокировка. Когда LOCK# установлен мастером, операции могут происходить

по любым адресам, кроме заблокированных.

IDSEL# in – выбор устройства инициализации. Сигнал

формируется главным мостом или мостом PCI-PCI для выбора устройства при записи

или чтении его памяти конфигурации.

DEVSEL# s/t/s – выбор устройства, для мастера этот сигнал

показывает, что устройство (цель) на шине выбрано, а для цели - что мастер

декодировал адрес и выбрал цель.

Следующая группа сигналов связана с арбитражем и используется

только инициаторами для захвата шины.

REQ# t/s – запрос. Показывает арбитру, что инициатор требует

шину PCI. Каждый инициатор устанавливает собственный REQ#.

GNT# t/s – разрешение, устанавливается арбитром и поступает

на вход соответствующего инициатора, которому этот сигнал принадлежит.

К сигналам, сообщающим об ошибках, относятся сигналы PERR# и

SERR#.

PERR# s/t/s – ошибка четности формируется агентом,

обнаружившим ошибку паритета. Минимальная продолжительность этого сигнала –

один такт для каждой фазы данных.

SERR# o/d – системная ошибка, сообщает об ошибке паритета

адреса, данных при выполнении на шине PCI специального цикла (передачи кодов

сообщений, указывающих на состояние процессора (агента шины PCI)).

Системную группу сигналов составляют сигналы CLK и RST#.

CLK in – тактовые импульсы, которые управляют по переднему

фронту формированием всех сигналов шины PCI, кроме сигналов сброса и

прерывания.

RST# in – сброс, устанавливает регистры в начальное

состояние.

В качестве необязательных сигналов рассмотрим только сигналы

прерывания.

INTA# o/d – прерывание А. Сигнал запроса прерывания для

однофункциональных агентов.

INTB# - INTD# o/d – запросы прерываний только для

многофункциональных агентов шины PCI.

Команды шины, передаваемые во время адресной фазы по линиям

C/BE#, показаны в табл. 5.1.

Таблица 5.1

|

КОД (C/BE)

|

НАЗНАЧЕНИЕ КОМАНДЫ

|

|

0000

|

Подтверждение прерывания

|

|

0001

|

Специальный цикл

|

|

0010

|

Чтение ввода/вывода

|

|

0011

|

Запись ввода/вывода

|

|

0100

|

Резерв

|

|

0101

|

Резерв

|

|

0110

|

Чтение памяти

|

|

0111

|

Запись в память

|

|

1000

|

Резерв

|

|

1001

|

Резерв

|

|

1010

|

Чтение конфигурации

|

|

1011

|

Запись конфигурации

|

|

1100

|

Многократное чтение памяти

|

|

1101

|

Цикл двойного адреса

|

|

1110

|

Линейное чтение памяти

|

|

1111

|

Запись в память и обнуление

|

Подтверждение прерывания – чтение (неявно адресованного)

системного контроллера прерывания. При выполнении команды адрес в

соответствующей фазе не используется, а во время фазы данных сигналы разрешения

байтов показывают размер возвращаемого вектора.

Специальный цикл обеспечивает простой механизм передачи

сообщений на PCI, например, состояния процессора или дополнительной

сигнализации между агентами шины PCI. Команда не содержит явного адреса и

передает сообщение всем агентам, среди которых находятся заинтересованные

агенты, обрабатывающие полученную информацию. Чтение ввода/вывода – команда

чтения данных агента, находящегося в адресном пространстве ввода/вывода. При

выполнении команды все 32 бита адреса должны быть дешифрированы и сигналы

C/BE(3-0)# указывают на размер передаваемых данных.

Запись ввода/вывода – эта команда выполняет запись данных в

выбранное устройство на шине PCI и в остальном совпадает с командой чтения

ввода/вывода. Здесь следует отметить, что большинство плат ввода/вывода шины

ISA используют 10-битный адрес.

Чтение памяти – чтение данных агента, расположенного в

адресном пространстве памяти.

Запись в память – команда, употребляющая адресное

пространство памяти.

Чтение конфигурации осуществляется из области конфигурации

требуемого агента. Агент выбран, если его IDSEL активен.

Запись конфигурации заключается в передаче данных в

конфигурационную память, выбранную сигналом IDSEL соответствующего агента.

Многократное чтение памяти используется мастером для частой

передачи больших массивов данных, если есть программно доступный буфер данных

(КЭШ).

Цикл двойного адреса необходим для выполнения передачи

64-битного адреса соответствующих агентов.

Линейное чтение памяти – команда, аналогичная команде чтения

памяти, за исключением того, что мастер реализует больше, чем две 32-битные

фазы данных. Эта команда применяется при частой передаче больших массивов данных.

Запись в память и обнуление позволяет оптимально использовать

память, гарантируя минимум передач для заполнения одной КЭШ, и требует размера

КЭШ, заданного в конфигурационном регистре.

На шине PCI используется пакетный основной принцип передачи

данных, состоящий из фазы адреса и одной или более фаз данных и применяемый в

пространстве памяти или ввода/вывода.

Формирование пакетов выполняет шлюз, стоящий между

процессором и шиной PCI, так как процессор в настоящее время реализует только

одну фазу данных. Если к шине PCI подключено устройство с одной фазой данных,

то оно (в случае многофазовой передачи) после первой фазы прерывает к себе

доступ. Для корректной работы устройства все доступы ввода/вывода появляются на

шине PCI, как только процессор сгенерирует их.

В пространстве ввода/вывода дешифрация адреса выполняется

каждым устройством PCI, причем младшие разряды адреса AD1 и AD0 позволяют

заранее (без задержки) определить разрешенный байт данных (табл. 5.2).

Таблица 5.2

|

AD1

|

AD0

|

C/BE3#

|

C/BE2#

|

C/BE1#

|

C/BE0#

|

|

0

|

0

|

*

|

*

|

*

|

0

|

|

0

|

1

|

*

|

*

|

0

|

1

|

|

1

|

0

|

*

|

0

|

1

|

1

|

|

1

|

1

|

0

|

1

|

1

|

1

|

Примечание: 0 – сигнал C/BE# активен,

* - безразличное состояние.

Устройства PCI , использующие адресное пространство памяти,

должны проверять младшие биты адреса AD1 и AD0, чтобы обеспечить нужный пакетный

порядок. Для доступа к 32-битным данным (DW) памяти употребляются разряды

адреса AD(31-2). При пакетной передаче необходимо после каждой фазы данных

выполнять линейный инкремент адреса, если биты AD1 и AD0 равны 0. Кроме того,

значение 01 соответственно этих же битов задает определенный режим переключения

ячеек КЭШ.

Управление пересылкой данных выполняется с помощью трех

сигналов: FRAME#, IRDY#, TRDY#. Сигнал FRAME# формируется мастером и указывает

начало и конец события на шине. Если сигналы FRAME# и IRDY# сняты (высокие

уровни), то интерфейс свободен (находится в пассивном состоянии).

Первый положительный (передний) фронт такта CLK определяет

фазу адреса, во время которой направляется адрес и код команды от мастера к

исполнителю. Если сигналы IRDY# и TRDY# имеют низкие (активные) уровни, то в

соответствующем такте CLK выполняется передача данных. Снятие любого из этих

сигналов вызывает появление тактов ожидания в работе мастера (приостанавливается

передача данных). Кроме того, следует отметить, что все сигналы выбираются по переднему

фронту сигнала CLK.

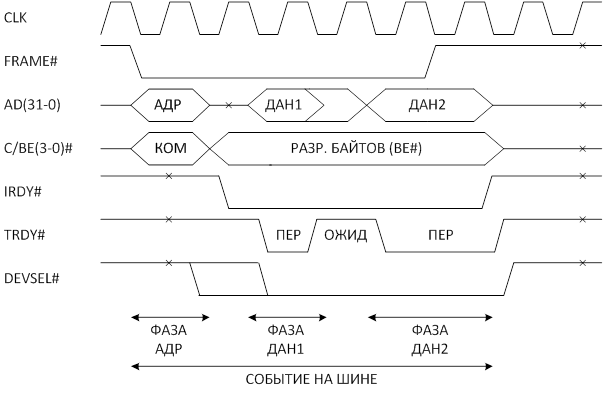

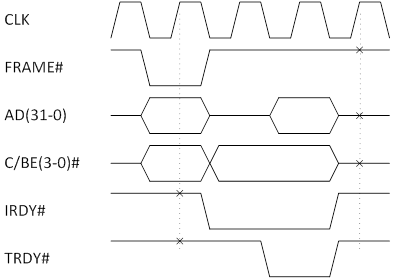

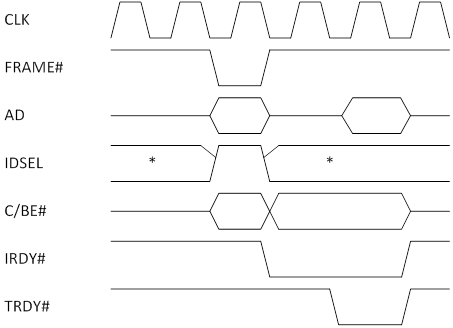

На рис. 5.2 представлена временная диаграмма чтения, в

которой для упрощения рисунка показаны две фазы передачи (ПЕР) данных (ДАН1 и

ДАН2) и один такт ожидания (ОЖИД), устанавливаемый мастером с помощью сигнала

TRDY#.

Обозначение

‘ x ‘ на диаграмме указывает на переключение сигнала на соответствующей линии

шины PCI, т.е. один агент прекращает управление сигналом, а другой начинает.

Исполнитель, опознав собственный адрес , устанавливает сигнал DEVSEL# и затем

направляет данные по шине AD(31-0) к мастеру. Сигнал DEVSEL# может быть

установлен перед передачей данных или одновременно с ними. Сброс сигнала

DEVSEL# совпадает со снятием сигнала TRDY#. В фазе данных сигналы C/BE# показывают

разрешенные (РАЗР) байты на шине AD(31-0). По данным пакета мастер узнает, что

следующая фаза последняя, и снимает сигнал FRAME#. Событие на шине завершается,

если FRAME# и IRDY# неактивны.

Рис.

5.2. Временная диаграмма чтения

Событие на

шине может быть прекращено по инициативе мастера или цели. Если событие завершается

мастером, то он снимает сигнал FRAME# при активном сигнале IRDY#, сообщая цели

о предстоящей финальной фазе данных. Эта последняя фаза данных происходит при

активных сигналах IRDY# и TRDY#. После чего сбрасывается сигнал IRDY# и вместе

с сигналом FRAME# он приобретает неактивный уровень, что означает пустое

состояние шины.

Для

прекращения события на шине со стороны цели используется сигнал STOP#, который

должен быть активным, пока FRAME# не станет пассивным.

В случае,

когда ни один исполнитель не отвечает мастеру, то он, если снят сигнал DEVSEL#,

завершает событие на шине, которое называется мастер-аборт, при этом

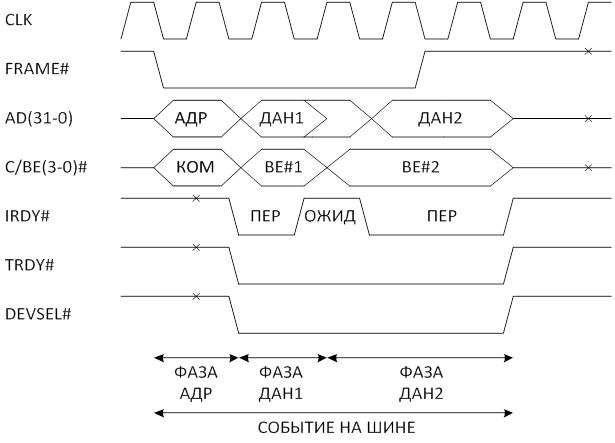

сбрасываются сигналы FRAME# и DEVSEL#. Временная диаграмма записи данных

изображена на рис. 5.3.

Запись

начинается установкой сигнала FRAME#. На рис. 5.3 показаны две фазы данных и

один такт ожидания, который устанавливается путем снятия мастером сигнала

IRDY#.

Рис.

5.3. Временная диаграмма запись

В основном

операция записи аналогична операции чтения за исключением того, что адрес и

данные устанавливаются мастером. Последняя фаза данных определяется тем, что

FRAME# пассивен, а IRDY# активен.

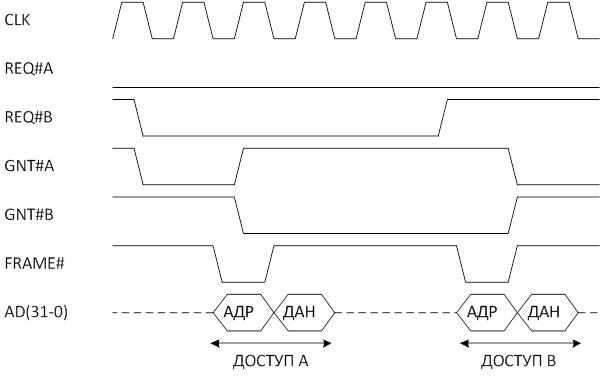

При наличии

нескольких инициаторов на шине PCI предусмотрена процедура централизованного

арбитража, которая возможна во время предыдущего доступа (скрытый арбитраж).

На рис. 5.4

показана временная диаграмма арбитража.

Диаграмма

иллюстрирует взаимодействие двух агентов А и В на шине PCI. Вначале агент А устанавливает

первым запрос REQ#A на управление шиной, поступающий в арбитр, и получает к ней

доступ с приходом сигнала GNT#A от арбитра. С этого момента времени агент А

формирует FRAME# и начинает передачу данных на шине. Сигнал REQ#A удерживается

агентом, который желает продолжить событие на шине. Когда FRAME# агента А

установлен, арбитр принимает запрос REQ#B агента В и сбрасывает сигнал GNT#A .

С поступлением этого сигнала агент А заканчивает передачу данных на шине и

снимает сигналы FRAME# и IRDY# (освобождает интерфейс).

-

Рис.

5.4. Временная диаграмма арбитража

При наличии

сигнала арбитра GNT#B активного (низкого) уровня и при выполнении условия

освобождения интерфейса агентом А (сигналы FRAME# и IRDY# имеют пассивный уровень)

управление интерфейсом получает агент В. Если запрос REQ#B агента В снят, то

это указывает арбитру на завершение события на шине агентом В и арбитр

обслуживает запрос агента А. Арбитр может снять GNT# какого-либо агента В в

любое время, если установлен более приоритетный запрос REQ# другого агента.

Шина PCI

реализует циклы подтверждения прерывания. Временная диаграмма цикла подтверждения

прерывания показана на рис. 5.5.

Временная

диаграмма выполняется при реализации инициатором команды подтверждения прерывания

(0000) после получения сигнала запрета прерывания. В фазе адреса инициатор

передает произвольное значение адреса и код команды (0000), а в фазе данных

исполнитель устанавливает вектор (младший байт), разрешение которого

определяется инициатором (1000). Исполнитель должен направить вектор

инициатору, когда установлены TRDY# и DEVSEL#.

Рис.

5.5. Временная диаграмма подтверждения прерывания

На шине PCI

выполняется контроль четности всеми агентами в фазах адреса и данных, причем

сигналы C/BE(3-0)# участвуют также при контроле. Сигнал PAR формируется

агентом, который управляет AD(31-0), и отстает на один такт от адреса или

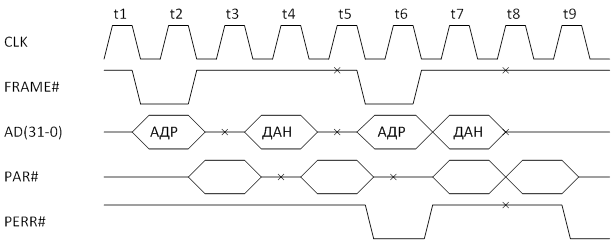

данных. На рис. 5.6 изображена временная диаграмма контроля четности при

выполнении операций чтения и записи данных.

Рис. 5.6. Временная диаграмма контроля четности

Во время

выполнения операции чтения инициатор вырабатывает сигнал PAR# для информации,

устанавливаемой во время фазы адреса (t3), и при записи для информации фазы адреса

(t7) и данных (t8), а исполнитель формирует PAR# во время ввода данных (t5) в

инициатор. В случае обнаружения ошибки паритета агент устанавливает сигнал

PERR#.

Рассмотрим

некоторые требования, предъявляемые к устройствам шины PCI. В качестве формирователей

(приемников) сигналов шины следует использовать элементы, которые не потребляют

ток в статическом состоянии, а потребляют его в моменты переключения. К таким

элементам относятся КМОП (комплиментарные полевые кремниевые элементы),

позволяющие существенно снизить потребление устройством энергии. Для построения

интерфейсных схем (контроллеров) можно использовать программируемые логические

интегральные схемы (ПЛИС), изготовленные по технологии КМОП, например ПЛИС

фирмы Xilinx, или отечественные аналоги, выпускаемые Воронежским НИИЭТ.

Во внешней

плате, подключаемой через слот (разъем) к шине PCI, большую часть тока потребляют

подтягивающие резисторы (2.7К при напряжении 5V), стабилизирующие значения сигналов

шины PCI. В слоте шины PCI имеются два контакта: PRSNT1# и PRSNT2#, коды на

входах которых используются для индикации внешней платы в слоте и определения

потребляемой мощности платой. Например, код 00 указывает, что внешняя плата

присутствует и потребляемая ею мощность 7.5W максимум. Таким образом, внешняя

плата должна указывать максимальную потребляемую мощность. Слоты подключаются к

четырем шинам питания: 5V, 3.3V, 12V и –12V. Максимальная потребляемая мощность

каждой внешней платой равна 25W. Формирователи должны иметь выходной ток

низкого уровня (без резистора) – 3 мА или 6 мА с резистором. Максимальная

емкость вывода компонента равна 10 пФ и максимальная длина дорожки от

соединителя платы до элемента не более 3.8 см. Шинный сигнал должен быть

ограничен одной нагрузкой.

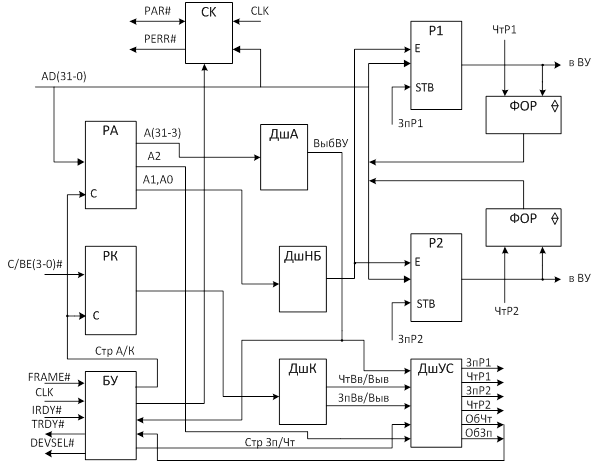

В заключение

этой темы рассмотрим подключение двух регистров Р1 и Р2, доступных по записи и

чтению, к шине PCI (рис. 5.7), причем с целью упрощения рисунка память

конфигурации не рассматривается.

Рис.

5.7. Структурная схема исполнителя шины PCI

Режим чтения

регистров Р1 и Р2 не является основным, а предусмотрен для проверки работы

регистров. Работа схемы описывается в соответствии с временными диаграммами

записи и чтения с одной фазой данных. Вначале инициатор устанавливает адрес на

шину AD(31-0), а затем – сигнал FRAME#, поступающий в блок управления (БУ). БУ

формирует сигнал строб адреса/команды (СтрА/К) по положительному фронту первого

CLK установленного FRAME#, т.е. когда сигналы адреса на линиях AD(31-0) и

команды на линиях C/BE(3-0)# являются стабильными. По сигналу СтрА/К происходит

запоминание адреса в регистре адреса (РА) и команды в регистре команды (РК).

Запоминание этой информации связано с тем, что минимальный период такта CLK

равен 30 нс и для гарантированной дешифрации адреса его не хватает. Обычно на

“медленных” мультиплексированных системных шинах A/D сначала дешифруют адрес, а

затем запоминают результат дешифрации и младшие биты адреса, выбирающие нужные

регистры в исполнителе. В схеме исполнителя дешифратор адреса (ДША) декодирует

общую старшую часть адреса и формирует сигнал выбора (ВыбВУ). Кроме того,

значения (0 и 1) бита адреса А2 осуществляют соответствующий выбор регистров Р1

и Р2. Биты адреса А1 и А0 с помощью дешифратора номера байта (ДшНБ) управляют

разрешением передачи соответствующего байта в формате данных. Кроме того,

дешифратор команд (ДшК) декодирует 4-битный код команды и формирует сигнал

чтения ввода/вывода (ЧтВв/Выв) или запись ввода/вывода (ЗпВв/Выв). Дешифратор

управляющих сигналов (ДшУс) в соответствии с входной информацией формирует

сигнал записи в Р1 (ЗпР1), чтения Р1 (ЧтР1) , ЗпР2, ЧтР2, общего чтения (ОбЧт)

или общей записи (ОБЗп). Сигнал ОбЧт вырабатывается, если установлен ЧтР1 или

ЧтР2. Для формирования сигналов ЧтР1,ЧтР2,ЗпР1,ЗпР2 в нужный момент времени БУ

вырабатывает сигнал строб записи/чтения (СтрЗп/Чт), если установлены сигналы

ВыбВУ, IRDY# и соответствующий импульс CLK. Передний фронт сигнала DEVSEL#

устанавливается одновременно с фронтом сигнала ВыбВУ, а задний фронт снимается,

как только будет снят сигнал IRDY# (см. рис. 5.2 и 5.3). При выполнении

операции чтения данных сигнал TRDY# устанавливается одновременно с передачей

данных от исполнителя к инициатору и сбрасывается после снятия инициатором

сигнала IRDY#.

Если выполняется операция записи данных в какой-либо регистр

исполнителя, то необходимо за 30 нс (до прихода данных) выполнить дешифрацию

адреса (сформировать сигнал ВыбВУ).

При отсутствии возможности выполнить это условие следует на

один такт задержать формирование TRDY#, т.е. ввести такт ожидания в работе

инициатора. В схеме не используется приемопередатчик данных, вносящий задержку

как, например, в контроллерах шины ISA, здесь вместо него применяются два

формирователя (ФОР) с тремя состояниями. Кроме того, при чтении данных схема

контроля (СК) формирует выходной сигнал PAR# , а при записи данных она

сравнивает входной сигнал PAR# с результатом проверки принимаемых данных на

четность. Если обнаружена ошибка, то устанавливается сигнал PERR#.

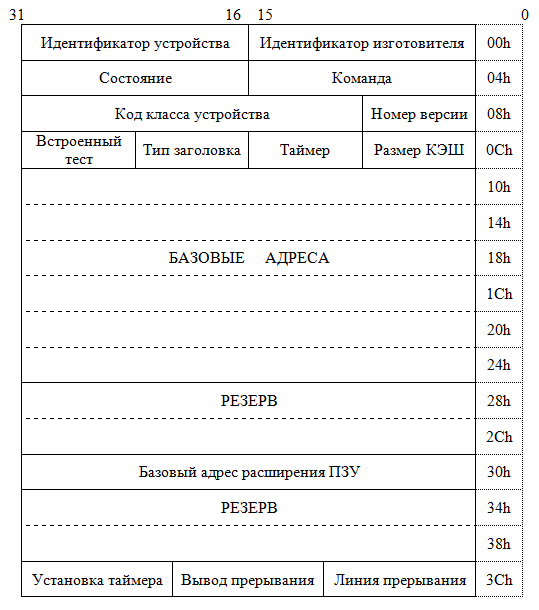

Стандарт шины PCI предусматривает наличие отдельного

адресного пространства конфигурации, используемого специальными программами.

Для выполнения автоконфигурации, обработки катастрофических ошибок,

инициализации устройств и мостов, подключенных к шине PCI, каждому устройству

отводится 256-байтная память, имеющая следующий формат заголовка конфигурации

(рис. 5.8).

В формате заголовка первые 16 байтов являются стандартными

для PCI устройств, а следующие 48 байтов могут иметь различные размещения в

зависимости от базовых функций этих устройств. Специфические (произвольные) сведения

об устройствах записываются в байтах памяти конфигурации в диапазоне 64-256.

Рис.

5.8. Формат заголовка конфигурации

Идентификаторы устройства и изготовителя определяют

соответственно тип (номер) устройства и его изготовителя.

В поле состояния (16-битном регистре состояния) отмечаются

события, происходящие на шине PCI, например, установка устройством сигнала

SERR# (системная ошибка), обнаружение устройством ошибки паритета (PAR),

завершение целью транзакции с ошибкой (адресат-аборт), завершение мастером

операции, на которую не отвечает цель (мастер-аборт) и т.д. Транзакция – событие

на шине, состоящее из фазы адреса и одной или нескольких фаз данных.

Поле команды (16-битный регистр команды) выполняет некоторое

управление работой устройства и использует младшие 10 битов, в которых

разрешаются или запрещаются доступы к вводу-выводу, шине PCI, памяти, регистрам

палитры видеоадаптера типа VGA и задаются другие функции управления.

Коды класса устройств содержат коды базового класса (старшие

байты со смещением 0Bh), которые на крупном уровне определяют классы устройств.

Различают следующие классы устройств и их коды: контроллеры

запоминающих устройств (01h), сетевые контроллеры (02h), дисплейные адаптеры

(03h), мультимедийные устройства (04h), контроллеры памяти (05h) и мосты (06h).

Средний байт (смещение 0Аh) кода класса содержит код

подкласса устройств. Например, для базового класса 01h контроллеру SCSI

соответствует подкласс 00h, контроллеру IDE – подкласс 01h, контроллеру гибкого

диска – подкласс 02h и т.д.

Младший бит (смещение 09h) определяет интерфейс

программирования на уровне регистра. Обычно этот байт равен 00h.

Базовый класс мостов (код 06h) имеет следующие подклассы:

главный мост (00h), ISA мост (01h), EISA мост (02h), MC мост (03h), PCI-PCI мост

(04h) и пр.

Номер версии задается изготовителем и может рассматриваться

расширением номера устройства. Управление встроенным тестом, если он есть,

осуществляется содержимым соответствующего регистра формата заголовка

конфигурации. Кроме того, в этом регистре отмечаются результаты тестирования

(биты завершения).

Тип заголовка указывает, является ли данное устройство

однофункциональным или многофункциональным и определяет структуру всех

остальных байтов формата заголовка, начиная с адреса 10h. Для приведенного

формата заголовка код типа заголовка равен 00h.

Таймер, входящий в состав заголовка, подсчитывает число

тактов шины PCI и определяет время, выделенное мастеру, для освобождения шины

при наличии других запросов на захват шины.

Размер КЭШ задается числом 32-битных данных и необходим с

целью определения границы пакетной передачи данных.

Базовые адреса позволяют определить наличие различных

устройств, присоединяемых к шине PCI, объем используемой памяти, адресное

пространство контроллеров ввода/вывода. Шесть 32-битных регистров отведены под

базовые адреса, начиная со смещения 10h. Бит 0 в базовых регистрах указывает на

его отношение к памяти (0) или вводу/выводу (1). В базовом регистре памяти

указывается расположение базового адреса, например, в 32-битных или 64-битных

адресных пространствах и значение базового адреса. Значение базового адреса

ввода/вывода хранится в соответствующем регистре базового адреса с битом 0,

равным 1.

Смещение 30h указывает на базовый адрес расширения ПЗУ и

разрешение дешифрации адреса.

Регистр установки таймера (2 байта) предназначен для задания

длительности пакетного периода и частоты доступа к шине PCI. В регистре вывод

прерывания (8 бит) определяется, какой сигнал прерывания используется

устройством, например, значение 1 соответствует сигналу INTA#, значение 2 –

сигналу INTB# и т.д. Регистр линии прерывания хранит информацию о соединении

вывода прерывания устройства со входом системного контроллера прерывания, т.е.

сообщается номер запроса системного контроллера прерывания.

Выбор адресного пространства конфигурации любого устройства

PCI выполняется с помощью интерфейсного сигнала IDSEL. Сигнал IDSEL формирует

главный мост (дизайнер системы) или мост PCI-PCI и этот сигнал достоверен

(устойчив) только в первом такте CLK установки сигнала FRAME# (в фазе адреса)

при выполнении команды конфигурации. Для расширения числа подключаемых к шине

устройств предусмотрена возможность соединения вывода IDSEL через резистор с

одной из старших адресных линий (не используемых при доступе к памяти конфигурации)

для выбора соответствующего устройства PCI. Каждый сигнал IDSEL выбирает

соответствующее ему устройство PCI.

Временная диаграмма чтения памяти конфигурации представлена

на рис. 5.9.

* - неопределенное состояние

Рис. 5.9. Чтение памяти конфигурации

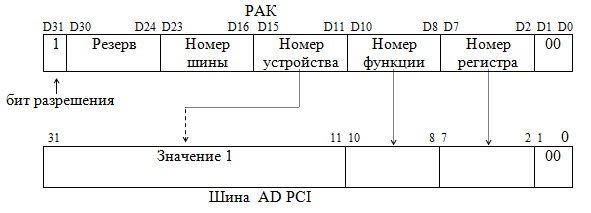

Так как шины PCI могут быть иерархического типа, состоящего

из нескольких шин, разделенных мостами, то предусмотрены 2 типа доступа (041)

со стороны моста (главного или PCI-PCI) к устройствам (целям) PCI. При доступе

типа 0 (в пределах одной шины PCI) мост содержит два порта: 32-битный регистр

адреса конфигурации (CF8h) и 32-битный регистр данных конфигурации (CFCh), с

помощью которых выполняется обращение к памяти конфигурации устройства PCI. В

регистре адреса конфигурации биты D1D0, равные значениям 00, определяют тип

доступа 0. Биты D7-D2 задают номер регистра памяти конфигурации, биты D10-D8 –

номер функции, если устройство PCI многофункциональное, и биты D15-D11 – номер

устройства PCI, который может быть преобразован только в одно единичное

значение в фазе адреса на одной из линий AD31-AD11 (сигнал IDSEL). На рис. 5.10

представлена схема трансляции содержимого регистра адреса конфигурации (РАК) на

линии AD(31-0) шины PCI.

Доступ типа 1 (доступ к устройству на другой шине)

определяется значениями битов D1 D0, равными 01. При этом обращении

используются в регистре PAR биты D23-D16, предназначенные для выбора одной из

128 шин системы.

Рис 5.10. Схема трансляции

содержимого РАК на шину AD

Разъем шины PCI показан на рис. 5.11, в котором для удобства

размещения номера выводов представлены в двух колонках.

|

Ряд В

|

Номер

|

Ряд А

|

Ряд В

|

Номер

|

Ряд А

|

|

-12 В

|

1

|

-TSTRES

|

-C/BE 3

|

26

|

IDSEL

|

|

Test Clock

|

2

|

+12 B

|

AD 23

|

27

|

+3,3 B

|

|

GND

|

3

|

TSTMSLCT

|

GND

|

28

|

AD 22

|

|

Test DO

|

4

|

Test DO

|

AD 21

|

29

|

AD 20

|

|

+5 B

|

5

|

+5 B

|

AD 19

|

30

|

GND

|

|

+5 B

|

6

|

-INTR A

|

+3,3 B

|

31

|

AD 18

|

|

-INTR B

|

7

|

-INTR C

|

AD 17

|

32

|

AD 16

|

|

-INTR D

|

8

|

+5 B

|

-C/BE 2

|

33

|

+3,3 B

|

|

-PRSNT 1

|

9

|

Reserved

|

GND

|

34

|

-FRAME

|

|

Reserved

|

10

|

+V I/O

|

-IRDY

|

35

|

GND

|

|

-PRSNT 2

|

11

|

Reserved

|

+3,3 B

|

36

|

-TRDY

|

|

GND / Ключ

|

12

|

GND / Ключ

|

-DEVSEL

|

37

|

GND

|

|

GND / Ключ

|

13

|

GND / Ключ

|

GND

|

38

|

-STOP

|

|

Reserved

|

14

|

Reserved

|

-Lock

|

39

|

+3,3 B

|

|

GND

|

15

|

-RST

|

ParityER

|

40

|

SDONE

|

|

Clock

|

16

|

+V I/O

|

+3,3 B

|

41

|

-SBOFF

|

|

GND

|

17

|

-GNT

|

SysERR

|

42

|

GND

|

|

-REQ

|

18

|

GND

|

+3,3 B

|

43

|

PAR

|

|

+V I/O

|

19

|

Reserved

|

-C/BE 1

|

44

|

AD 15

|

|

AD 31

|

20

|

AD 30

|

AD 14

|

45

|

+3,3 B

|

|

AD 29

|

21

|

+3,3 B

|

GND

|

46

|

AD 13

|

|

GND

|

22

|

AD 28

|

AD 12

|

47

|

AD 11

|

|

AD 27

|

23

|

AD 26

|

AD 10

|

48

|

GND

|

|

AD 25

|

24

|

GND

|

GND

|

49

|

AD 9

|

|

+3,3 B

|

25

|

AD 24

|

GND / Ключ

|

50**

|

GND / Ключ

|

|

GND / Ключ

|

51****

|

GND / Ключ

|

GND

|

73

|

AD 56

|

|

AD 8

|

52

|

-C/BE

|

AD 55

|

74

|

AD 54

|

|

AD 7

|

53

|

+3,3 B

|

AD 53

|

75

|

+V I/O

|

|

+3,3 B

|

54

|

AD 6

|

GND

|

76

|

AD 52

|

|

AD 5

|

55

|

AD 4

|

AD 51

|

77

|

AD 50

|

|

AD 3

|

56

|

GND

|

AD 49

|

78

|

GND

|

|

GND

|

57

|

AD 2

|

+V I/O

|

79

|

AD 48

|

|

AD1

|

58

|

AD 0

|

AD 47

|

80

|

AD 46

|

|

+V I/O

|

59

|

+V I/O

|

AD 45

|

81

|

GND

|

|

-ACK 64

|

60

|

-REQ 64

|

GND

|

82

|

AD 44

|

|

+5 B

|

61

|

+5 B

|

AD 43

|

83

|

AD 42

|

|

+5 B

|

62

|

+5 B

|

AD 41

|

84

|

+V I/O

|

|

|

|

GND

|

85

|

AD 40

|

|

|

|

AD 39

|

86

|

AD 38

|

|

Reserved

|

63

|

GND

|

AD 37

|

87

|

GND

|

|

GND

|

64

|

-C/BE 7

|

+V I/O

|

88

|

AD 36

|

|

-C/BE

|

65

|

-C/BE 5

|

AD 35

|

89

|

AD 34

|

|

-C/BE

|

66

|

+V I/O

|

AD 33

|

90

|

GND

|

|

GND

|

67

|

PAR 64

|

GND

|

91

|

AD 32

|

|

AD 63

|

68

|

AD 62

|

Reserved

|

92

|

Reserved

|

|

AD 61

|

69

|

GND

|

Reserved

|

93

|

GND

|

|

+V I/O

|

70

|

AD 60

|

GND

|

94

|

Reserved

|

|

AD 59

|

71

|

AD 58

|

|

|

|

|

AD 57

|

72

|

GND

|

|

|

|

Примечание: *12,13 – ключ для 3,3 В; **50,51 – ключ для 5

В.

Рис. 5.11. Разъем шины PCI

Похожие материалы:

Логическая модель макроэкономики

Алесинская Т.В. Основы логистики: Логистический процесс на складе

Логистические системы

Локальные нормативные акты,

содержащие нормы трудового права

Гончарук В.А. Развитие предприятия: Локальные цели и системный подход

Ломщик пода

|