|

В.А. Авдеев, В.Ф. Гузик

Компьютеры: шины, контроллеры, периферийные устройства

Учебное пособие. Таганрог: ТРТУ, 2001. - 536 с.

6. Периферийные интерфейсы

6.6. Подключение портов к шине ISA

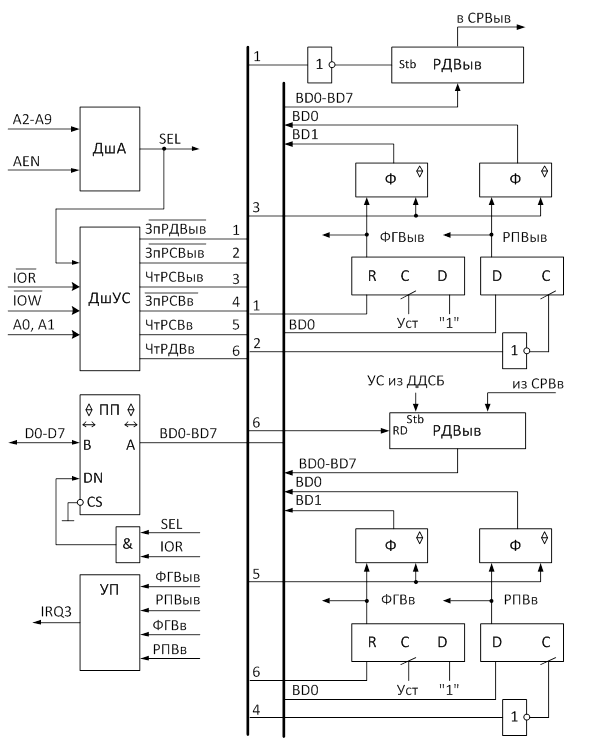

На рис. 6.15 показана структурная схема сопряжения портов

асинхронных передатчика и приемника с шиной ISA. В следующей табл. 6.3

перечислены порты и указаны их адреса, взятые из карты распределения адресного

пространства ввода-вывода для второй асинхронной передачи.

Для выбора устройства используются старшие разряды адреса

А2-А9, являющиеся общими для всех портов (01111101), а для выбора порта внутри

устройства – младшие разряды адреса А0, А1.

Рис.6.15.

Структурная схема сопряжения портов с шиной ISA

Таблица 6.3

|

Порт

|

Режим

|

Адрес

|

Сигнал ДшУС

|

|

РД Выв

|

Запись

|

2F8H

|

|

|

РД Вв

|

Чтение

|

2F8H

|

Чт РД Вв

|

|

РС Выв

|

Запись

|

2F9H

|

|

|

РС Выв

|

Чтение

|

2F9H

|

Чт РС Выв

|

|

РС Вв

|

Запись

|

2FAH

|

|

|

РС Вв

|

Чтение

|

2FAH

|

Чт РС Вв

|

Регистру РД Выв (РД Вв) соответствуют разряды А0=А1=1,

регистру РС Выв – разряды А0=1 и А1=0, а регистру РС Вв – разряды А0=0 и А1=1.

В режиме вывод процессор устанавливает адрес на шину адреса

А0-А9 и данные на шину данных D0-D7. Старшие разряды адреса А2-А9 и сигнал

разрешения адреса (AEN) декодируются дешифратором адреса (ДшА), формирующим на

выходе сигнал выбора устройства (SEL). Низкий уровень сигнала AEN указывает на

обычный ввод-вывод, а высокий уровень – на режим прямого доступа к памяти. Байт

данных с системной шины D0-D7 поступает на внутреннюю шину данных BD0-BD7, так

как на входе DN приемопередатчика (ПП) установлен низкий уровень (сигнал

IOR=0). В качестве ПП в схеме применяется микросхема 580ВА86, в которой

осуществляется передача с шины BD0-BD7 на шину D0-D7 (A®B), если сигнал на входе DN=1. Через 92 нс, после того как

гарантированно установлен адрес, процессор выдает управляющий сигнал  , поступающий на вход дешифратора

управляющих сигналов (ДшУС). Дешифратор ДшУС с учетом разрядов адреса А0, А1 и

сигнала SEL формирует на соответствующем выходе сигнал записи в порт, например,

ЗпРДВыв. Таким образом, сигнал ЗпРДВыв=SEL*`A0*`A1*IOW. , поступающий на вход дешифратора

управляющих сигналов (ДшУС). Дешифратор ДшУС с учетом разрядов адреса А0, А1 и

сигнала SEL формирует на соответствующем выходе сигнал записи в порт, например,

ЗпРДВыв. Таким образом, сигнал ЗпРДВыв=SEL*`A0*`A1*IOW.

Запись данных в порты происходит по спаду (снятию) сигнала  . Данные

сохраняются в течение 185 нс после окончания сигнала . Данные

сохраняются в течение 185 нс после окончания сигнала  . .

Системная шина ISA относится к синхронным интерфейсам,

поэтому сигнал квитирования, указывающий на завершение операции ввода-вывода

данных, отсутствует.

Аналогичным образом выполняется операция чтения данных.

Процессор устанавливает адрес на шину А0-А9. Устройство обнаруживает свой

адрес, формируя на выходе ДшА сигнал SEL. Затем через 92 нс процессор выдает

управляющий сигнал чтения ( ). Дешифратор ДшУС по фронту сигнала ). Дешифратор ДшУС по фронту сигнала  формирует

на одном из выходов сигнал чтения порта, например, сигнал Чт РД Вв, по которому

выполняется передача содержимого регистра РДВв на системную шинуD0-D7 через ПП,

открытый для передачи данных в направлении от А к В (сигнал на входе DN=1). формирует

на одном из выходов сигнал чтения порта, например, сигнал Чт РД Вв, по которому

выполняется передача содержимого регистра РДВв на системную шинуD0-D7 через ПП,

открытый для передачи данных в направлении от А к В (сигнал на входе DN=1).

В схеме содержится узел

прерывания (УП), который формирует сигнал прерывания IRQ3, соответствующий

второму асинхронному порту, при наличии пары сигналов ФГ Выв и РП Выв или ФГ Вв

и РП Вв.

Установка бита РП

выполняется путем использования бита данных BD0 и адреса регистра состояния, т.

е. этот бит является портом с передачей бита данных.

Похожие материалы:

Подключение КНГМД к шине

Подинщик (Выпуск №17 ЕТКС)

Поддувщик изделий

Подкуп избирателей, участников

референдума либо осуществление в период избирательной кампании, кампании

референдума благотворительной деятельности с нарушением законодательства о

выборах и референдумах

Подкуп или принуждение к

даче показаний или уклонению от дачи показаний либо к неправильному переводу - ст.309 УК РФ

Подкуп участников и организаторов

профессиональных спортивных соревнований и зрелищных коммерческих конкурсов

|