|

В.А. Авдеев, В.Ф. Гузик

Компьютеры: шины, контроллеры, периферийные устройства

Учебное пособие. Таганрог: ТРТУ, 2001. - 536 с.

6. Периферийные интерфейсы

6.5. Асинхронный приемник

Асинхронный приемник выполняет прием последовательной

кодовой посылки, имеющей стартстопный формат, и преобразование

последовательного 8-разрядного кода в параллельный. Запуск асинхронного

приемника осуществляется стартовым битом. Процессор определяет, что регистр данных

ввода (РДВв) полон через прерывание или опрос бита ФГ регистра состояния.

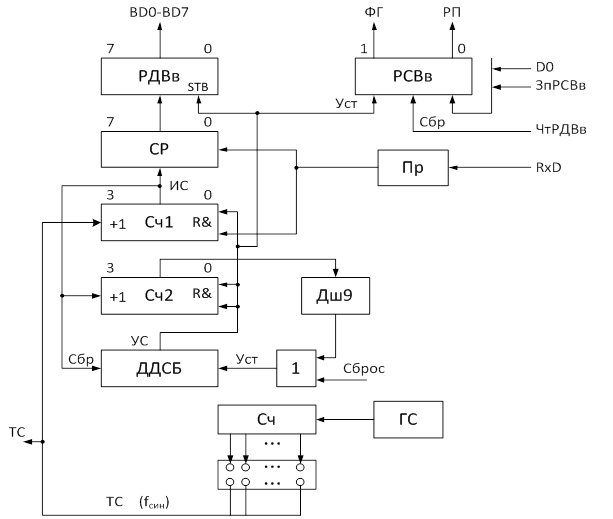

Структурная схема асинхронного приемника изображена на рис.

6.14. Принцип работы асинхронного приемника заключается в следующем.

Рис.

6.14. Структурная схема асинхронного приемника

Поступающий с линии данных RxD стартовый бит низкого уровня

разрешает работу счетчика Сч1 ( подсчет сигналов ТС),имеющего два сбросовых

входа, включенных по схеме &. Сброс счетчиков Сч1 и Сч2 выполняется, если

на обоих входах присутствуют сигналы высокого уровня. Таким образом, на первый

вход R счетчика Сч1 подан сигнал низкого уровня стартового бита, а на втором

входе R сохраняется сигнал высокого уровня с дискриминатора длительности

стартового бита (ДДСБ), реализованного на базе триггера. Предварительно (перед

началом работы устройства) ДДСБ был установлен в единичное состояние сигналом

Сброс.

Если на линии RxD вместо стартового бита присутствует

кратковременная помеха низкого уровня, то счетчик Сч1 не успеет подсчитать восемь

сигналов ТС (половина интервала бита) и на его выходе 8 (8-вес разряда) не

появится импульс сдвига (ИС). В случае поступления стартового бита счетчик Сч1

формирует первый импульс ИС, который записывает стартовый бит в сдвиговый

регистр (СР) и сбрасывает триггер ДДСБ. Теперь на выходе ДДСБ вырабатывается

управляющий сигнал (УС) низкого уровня, поступающий на второй сбросовый вход

счетчика Сч1 и разрешающий дальнейший прием последовательной кодовой посылки в

СР. Ввод кодовой посылки осуществляется через усилитель-приемник (ПР). Кроме

того, выходной сигнал триггера ДДСБ разрешает работу счетчика Сч2,

подсчитывающего импульсы ИС. Как только содержимое счетчика Сч2 станет равным 9

(1001), на выходе дешифратора Дш9 вырабатывается сигнал, указывающий на завершение

приема последовательной кодовой посылки и устанавливающий триггер ДДСБ в

единичное состояние. Высокий уровень выходного сигнала триггера ДДСБ

переписывает содержимое регистра СР в регистр РДВв и устанавливает бит ФГ регистра

РС. Через прерывание (РП=ФГ=1) или опрос ФГ=1 (РП=0) процессор считывает

содержимое регистра РДВв. Чтение регистра РДВв выполняется сигналом Чт РДВ, который,

кроме того, осуществляет сброс бита ФГ регистра РСВв. После ввода следующей

последовательной кодовой посылки вновь устанавливается бит ФГ, указывающий на

то, что РДВв полон. После чтения содержимого РДВв происходит сброс бита ФГ и

т.д.

Формирование сигналов ТС для асинхронных передатчика и

приемника выполняется с помощью схемы, содержащей генератор сигналов (ГС),

счетчик (Сч) и наборное поле. Выходы Сч, осуществляющего деление частоты,

подключены ко входам наборного поля. Установив перемычку в наборном поле, можно

задать определенную частоту сигналов ТС (скорость передачи битов).

Похожие материалы:

Асинхронный передатчик

Асинхронная передача данных - Авдеев В.А. и др., 2001

Асимптотический линейный регрессионный анализ для интервальных данных

Аспираторщик

Ассистент инспектора фонда (Квалификационный справочник)

Ассортимент товаров

|