|

В.А. Авдеев, В.Ф. Гузик

Компьютеры: шины, контроллеры, периферийные устройства

Учебное пособие. Таганрог: ТРТУ, 2001. - 536 с.

6. Периферийные интерфейсы

6.4. Асинхронный передатчик

Рассмотрим устройство и работу УАПП, содержащего передатчик

и приемник.

Асинхронный передатчик выполняет преобразование

параллельного кода в последовательный со стартстопном форматом. Кроме того,

асинхронный передатчик через прерывание (установку флага готовности)

сигнализирует процессору о возможности вывода очередного символа.

Термины Ввод или Вывод рассматриваются относительно

процессора, т.е. процессор выводит байт данных и записывает в порт устройства

или процессор читает содержимое порта устройства и вводит в собственные

регистры. Асинхронный передатчик включает в себя два адресуемых порта:

8-разрядный регистр данных вывода (РДВыв) и 2-разрядный регистр состояния вывода

(РСВыв). Первый бит РСВыв доступен по записи и чтению со стороны процессора.

Выходной сигнал этого бита разрешает прерывание (РП) со стороны асинхронного

передатчика. Второй бит устанавливается асинхронным передатчиком, когда РДВыв

пуст, и имеет название Флаг готовности (ФГ). После того как символ будет

переписан в сдвиговый регистр (СР), асинхронный передатчик устанавливает бит

ФГ, что указывает процессору о возможности вывода очередного символа.

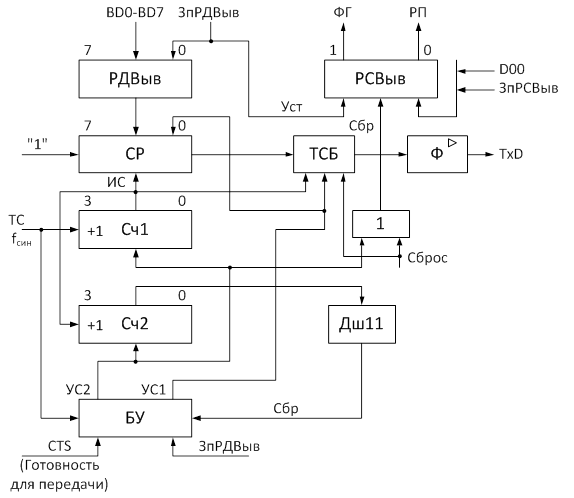

На рис.6.13 представлена структурная схема асинхронного

передатчика, в которой с целью её упрощения отсутствует схема контроля и

возможность программирования числа передаваемых бит данных и множителя скорости

(Мн=16). Поэтому на выходе ТхD асинхронного передатчика формируется

последовательная кодовая посылка, содержащая 11 бит (стартовый бит, 8

информационных и 2 стоповых бита).

Рис.

6.13. Структурная схема асинхронного передатчика

При включении питания по сигналу Сброс устанавливается бит

ФГ РСВыв, указывающий процессору, что РДВыв пуст. Процессор определяет это

состояние РДВыв через прерывание (РП=ФГ=1) или путем опроса ФГ (РП=0) регистра

состояния. Затем процессор выполняет вывод байта данных, который записывается в

РДВыв сигналом Зп РДВыв (схема сопряжения передатчика с системной шиной будет

рассмотрена ниже). Кроме того, сигнал Зп РДВыв осуществляет сброс бита ФГ РСВыв

и пуск блока управления (БУ) при наличии сигнала CTS (Готовность для передачи),

приходящего из внешнего устройства, которому передается последовательная

кодовая посылка.

БУ, синхронизированный тактовыми сигналами (ТС),

вырабатывает два управляющих сигнала: УС1 и УС2. Первым сигналом УС1

осуществляется сброс триггера стартового бита (ТСБ), предварительно

установленного в единичное состояние сигналом Сброс, и передача содержимого

РДВыв в СР. Вторым сигналом УС2 выполняются следующие действия: разрешается

работа счетчиков Сч1 и Сч2 и устанавливается бит ФГ РСВыв. Для построения БУ

используется два триггера.

Счетчик (4-разрядный Сч1) начинает подсчитывать сигналы ТС.

После приема восьми сигналов ТС (середина бита кодовой посылки) на четвертом

выходе Сч1(соответствующего весу 8) формируется импульс сдвига (ИС),

поступающий на СР и ТСБ и выполняющий сдвиг на один разряд девяти битов

последовательной кодовой посылки, причем первым через формирователь (Ф) на

линию TxD поступает стартовый бит. Таким образом, 4-разрядный счетчик Сч1

определяет Мн=16, т.е. длительность каждого бита кодовой посылки соответствует

шестнадцати сигналам ТС.

Счетчик Сч2 подсчитывает сигналы ТС. Как только содержимое

Сч2 станет равным коду 11 (1011), дешифратор (Дш11) этого кода формирует сигнал

Сбр, указывающий на завершение передачи 11-разрядной кодовой посылки. Последние

2 стоповых бита образуются за счет подключения последовательного входа СР к

напряжению, соответствующему логической единице (“1”). Сигнал дешифратора Дш11

выполняет сброс БУ, который, в свою очередь, запрещает работу счетчиков Сч1 и

Сч2. На этом завершается цикл передачи байта данных на линию TxD.

Похожие материалы:

Асинхронная передача данных

Теория принятия решений: Асимптотический линейный регрессионный анализ для интервальных данных

Асимптотическая теория одноступенчатых планов статистического контроля

Асинхронный приемник

Аспираторщик (Часть №2 выпуска №40 ЕТКС)

Ассистент инспектора фонда

|