|

В.А. Авдеев, В.Ф. Гузик

Компьютеры: шины, контроллеры, периферийные устройства

Учебное пособие. Таганрог: ТРТУ, 2001. - 536 с.

9. Устройство отображения информации

9.4. Адаптер VGA

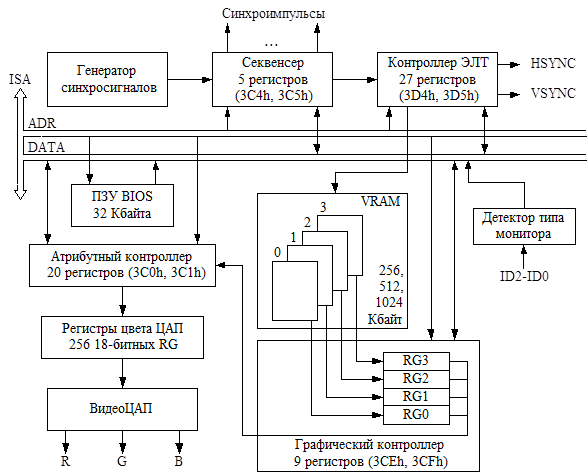

Структурная

схема адаптера VGA представлена

на рис. 9.5.

Адаптер

VGA содержит ПЗУ, например микросхему

127256 (Intel), имеющую емкость 32 Кбайта и

хранящую систему BIOS, которая

поддерживает функционирование процессора с адаптером VGA. Начальный адрес ячеек ПЗУ равен C000:0000h, а конечный адрес – 1000:3FFFh.

BIOS имеет следующие

основные компоненты: программу инициализации адаптера, драйверы управления

работой адаптера, наборы знакогенераторов для различных режимов с матрицами 8´8, 8´14 и 9´16 и таблицы видеопараметров для

задания специальных режимов БИС адаптера.

Рис.

9.5. Структурная схема адаптера VGA

Секвенсер (контроллер синхронизации) координирует работу

всех блоков адаптера. В состав секвенсера входят пять программно-доступных

регистров, с помощью которых задаются режимы синхронизации, режимы работы

видеопамяти (VRAM), выбор банка VRAM

и т.д. Доступ к регистрам осуществляется через порт 3C4h (индекса) и порт 3C5h (данных).

Секвенсер

обеспечивает циклический доступ процессора к банкам памяти во время обратного

хода луча по строке экрана. Для обращения процессора к VRAM секвенсер формирует сигнал готовности (I/O CH RDY).

В

адаптерах MDA и CGA в качестве контроллера электронно-лучевой трубки (ЭЛТ) используется

микросхема 6845 фирмы Motorola, предназначенная для управления формированием

сигналов HSYNC и VSYNC, курсора и изменения адреса видеопамяти синхронно с

образованием растра. Эта микросхема содержит 18 программно-доступных регистров,

обращение к которым выполняется с помощью двух портов (регистра индекса, 3D4H и

регистра данных, 3D5H). В контроллере ЭЛТ четыре регистра (R0–R3) используются

для задания параметров строчной развертки (число символов в строке, ширина и

начальная позиция HSYNC). Кроме того, четыре регистра (R4–R7) определяют

характеристики кадровой развертки (число строк, ширина VSYNC и т.д.). Два

регистра R8 и R9 предназначены соответственно для управления чересстрочным

режимом и хранения адреса конечной строки растра. Регистры R0–R9

инициализируются BIOS при включении питания. При смене режимов BIOS

модифицирует эти регистры. Регистры R10 (начальная строка) и R11 (конечная

строка) применяется для программирования формы курсора, а регистры R12 (старший

байт) и R13 (младший байт) отслеживают стартовый адрес выводимого на экран

символа. Адрес позиции курсора указывают регистры R14 (старший байт) и R15

(младший байт), а адрес позиции светового пера – R16 и R17. Регистры R12 и R13

могут быть использованы для выполнения горизонтального и вертикального сдвигов

изображения на экране.

В адаптере EGA применяется БИС, сохраняющая регистры

микросхемы 6845 и имеющая дополнительные регистры. Эта БИС формирует сигнал

прерывания (INTR) в момент времени начала вертикального гашения луча (обратного

хода), сообщая П о возможности доступа к видеопамяти. Кроме того, БИС позволяет

осуществлять доступ к двум несмежным областям видеопамяти. Каждый регистр БИС дополнен

девятым битом переполнения.

В адаптере VGA (СБИС) также сохраняется преемственность с

БИС ЭЛТ EGA (сохранены программно-доступные регистры, обращение к которым

выполняется с помощью портов 3D4H и 3D5H). Кроме того, введены дополнительные

регистры, связанные с реализацией новых режимов, содержащих 400 и 480 строк. Большая

часть регистров доступна по записи и по чтению со стороны П и регистры

развертки можно защитить от записи информации. Адаптер VGA может эмулировать

работу адаптера CGA, при этом в текстовом режиме повторяется каждая строка

(процесс двойного сканирования), т.е. символ с позицией 8´8 при двойном сканировании имеет

позицию 8´16.

Видеобуфер или видеопамять (VRAM) использует часть адресного

пространства системного П и расположен в видеоадаптере. Доступ к видеобуферу со

стороны П может быть прямой (непосредственный), реализуемый в адаптерах MDA и

CGA, и косвенный с использованием регистров-защелок, применяемый в адаптерах

EGA и VGA. Для получения немерцающего изображения контроллер ЭЛТ адаптера

периодически считывает содержимое видеобуфера с частотой 50–70 Гц и преобразует

его в видеосигнал (цифровой или аналоговый), поступающий в монитор. Емкость

видеобуфера находится в интервале от 4 Кбайт (MDA) до 256 (512) Кбайт (VGA).

Рассмотрим адресацию видеобуфера. В адаптере MDA 4 Кбайт

занимают неизменяемое адресное пространство от B000:0000h,

а в адаптере CGA 16 Кбайт – от В800:0000h. В адаптере

EGA используется 4 области адресного пространства в зависимости от битов 3 и 2

шестого вспомогательного регистра графического контроллера. Если эти биты принимают

значения 00 или 01, то адресный диапазон начинается от А000:0000h. Коды 10 или 11 указанных битов соответственно определяют

адресный диапазон от В000:0000h или В800:0000h. Для исключения всего видеобуфера из адресного пространства

П следует сбросить бит 1 выходного регистра (порта 3С2Н). Управление выбором

адресного пространства VGA выполняется так же, как и в EGA за исключением

разрешения (запрещения) адресации. В текущий момент времени обычно на экран

выводится только часть информации видеопамяти, называемой экранной страницей.

Если емкость видеобуфера равна 16 Кбайтам (CGA), то для текстового режима 80´25 видеобуфер содержит четыре страницы

(80´25´2=4 Кбайт). В текстовом режиме в видеобуфере хранится код

символа и код атрибута (2 байта). Для построения видеобуфера применяются

микросхемы памяти, имеющие два независимых (параллельных) канала доступа к ее

ячейкам. Один канал используется П для записи или чтения содержимого

видеобуфера, а другой необходим контроллеру ЭЛТ для регенерации изображения на

экране.

В адаптерах EGA и VGA

применяется графический контроллер для управления передачей данных между

видеобуфером и П, между видеобуфером и атрибутным контроллером. Графический

контроллер содержит 9 программно доступных регистров, обращение к которым

выполняется с помощью портов 3СЕН (индекса) и 3СFh

(данных). Атрибутный контроллер в адаптере VGA преобразует символьные атрибуты

текстового режима и пикселные данные графического режима в восьмиразрядные

индексы для выбора регистра цвета ЦАП. Доступ к 20‑ти регистрам

атрибутного контроллера осуществляется через порты 3С0h

(индекса) и 3С1h (данных).

Похожие материалы:

Адаптация персонала

Адаптация и адаптивный подход в управлении компаниями - Тычинский, 2006

Аграрная реформа в России 1906 г.

Адаптер принтера

Адвокатура в Российской Федерации (Батычко В.Т., 2009)

Административная

ответственность должностных лиц

|