|

В.А. Авдеев, В.Ф. Гузик

Компьютеры: шины, контроллеры, периферийные устройства

Учебное пособие. Таганрог: ТРТУ, 2001. - 536 с.

Приложение В. Проверочные задания, основные сведения и примеры программ

Режим прямого доступа к памяти

11.1. Формулировка задания

Разработать программу на

ассемблере, выполняющую проверку контроллера прямого доступа (КПДП) в режиме

записи (чтения) без передачи данных. После окончания заданного числа циклов ПДП

необходимо вывести на экран дисплея содержимое регистра состояния, регистра

текущего адреса и регистра текущего числа циклов.

11.2. Основные сведения

Основные сведения режима прямого доступа к памяти изложены в

главе 3.

Здесь дополнительно рассмотрим один из вариантов построения

структурной схемы КПДП, в которой с целью ее упрощения отсутствует регистр

управления, маскирования, программного запроса и обмена данными в режиме

память-память, имеющиеся в наличии в микросхеме I8237. Кроме того, в схеме не

реализуется функция циклического приоритетного доступа внешних устройств и

опущены некоторые мелкие детали. Эта структурная схема позволяет рассмотреть

принцип построения относительно сложной микросхемы, обслуживающей четыре канала

прямого доступа. Структурная схема КПДП (рис. 1) содержит следующие блоки.

ПП1 – двунаправленный 8-битный приемопередатчик,

предназначенный для управления направлением передачи данных и согласования

электрических характеристик системной шины данных ISA SD7 – SD0 и внутренней

шины данных BD7 – BD0.

РР3 – РР0 – блок регистров режима с

раздельной записью чтением. Выбор нужного регистра выполняется 2-битным кодом

номера канала (НКi). В формате регистра режима задается режим

(проверка, запись, чтение), инкремент (INC) или декремент (DEC),

автоинициализация и т.д.

ФУС – формирователь управляющих сигналов вырабатывает

следующие сигналы: чтение (-MRD) и запись (-MWD) оперативной памяти, чтение (-IORD)

и запись (-IOWD) ввода/вывода.

Пер – передатчик осуществляет вывод интерфейсных сигналов:

-MEMR, -MEMW, -IOR, -IOW, A19-A16 на соответствующие линии шины расширения

ISA.

Рис.1. Структурная

схема КПДП

Пр – приемник, характеризуется малым потреблением тока,

предназначен для усиления принимаемых сигналов.

РС3 – РС0 – блок регистров страницы с

разделенной записью и чтением, предназначен для временного хранения старшей

части адреса (А16-А19) каждого канала (К3-К0).

ФDACK – формирователь DACK в зависимости от кода номера

канала (НКi) вырабатывает активный низкий уровень одного из сигналов

подтверждения ПДП (-DACK3,...-DACK0).

РС – 8-битный регистр состояний, хранящий сигналы окончания

счета (Т/С) и сигналы наличия запросов DRQ для каждого канала (Кi).

БР1 – буферный регистр, выполняет запоминания

соответствующих входных сигналов запросов DRQ3-DRQ0, А3-А0 и т.д. на время

цикла ПДП.

Поступление новых сигналов может быть заблокировано сигналом

с выхода триггера включения (ТВкл).

Шиф – шифратор, выполненный на базе ПЗУ и предназначенный с

учетом 8-битной входной информации, поступающей на его адресные входы, для

формирования: кода номера канала (НКi); кода номера регистра (НР);

3-битного кода режима КПДП и сигнала включения (Вкл) КПДП. Коды номера канала

необходимы для выбора соответствующих регистров и имеют следующее представление:

00-канал 0, 01-канал 1, 10-канал 2 и 11-канал 3. Код номера регистра

дополнительно определяет адресные порты, например, регистр режима (РР), триггер

первый/последний (Тп/п) и т.д. Код режима является частью адресной

информации памяти микрокоманд (ПМ) и задает следующие режимы КПДП для каждого

канала в режиме связи с системным процессором:

-

запись и чтение

адреса;

-

запись и чтение

кода числа циклов.

ТВкл – триггер включения, выполняет блокирование поступления

новых запросов в БР1 до конца выполнения режима, сброс счетчика

микрокоманд (СчМ) и разрешения работы дешифратора команд (ДшК).

ДшК – дешифратор команд, выполняет декодирование 3-битовых

команд ПМ и формирует следующие сигналы: запись и чтение младшего байта, запись

и чтение старшего байта, конец режима и разрешение работы дешифратора

управляющих сигналов (ДшУС).

БР2 – буферный регистр, предназначен для хранения

системных сигналов –HLDA (подтверждение шины) и I/O CHRDY (готовности

канала ввода/вывода).

ПМ – память микрокоманд, реализованная на базе ПЗУ и

формирующая сигналы: HRQ (запрос шины), -AEN (разрешение адреса), 3-битный код

команд и т. д.

СчМ – счетчик микрокоманд, необходимый для формирования

последовательных адресных кодов ПМ в циклах ПДП, а также чтения и записи

16-битовой информации в КПДП со стороны системного процессора.

Тп/п

– триггер первый/последний, указывает на запись или чтение старшего или

младшего байтов данных, меняет свое состояние при каждом доступе к 16-битным

регистрам текущего адреса (РТА) или текущего числа циклов (РТЧЦ).

Т3 ПДП – триггер запрета ПДП, устанавливаемый по сигналу

RESET в единичное состояние для запрещения ПДП. Разрешить ПДП можно по команде

OUT c адресом 008h, причем бит данных BD2 должен быть равен 0.

ДшУС – дешифратор управляющих сигналов, который по номеру

регистра, поступающему из Шиф, формирует сигналы: запись в регистр режима

(-ЗпРР), запись в триггер запрета ПДП (-ЗпТЗ ПДП), сброс триггера первый/последний

(Сбр Тп/п) и запись в триггер Тп/п (-Зп Тп/п).

РТА3–РТА0 и РБА3–РБА0 – соответственно блок 16-битных

регистров текущего адреса и регистров базового адреса и регистров базового

адреса каналов К3-К0, предназначенных для приема со

стороны системного процессора начального адреса оперативной памяти. В циклах

ПДП содержимое РТА3-РТА0 меняется с помощью счетчика Сч путем

пересылки данных.

РТЧЦ3–РТЧЦ0 и РБЧЦ3–РБЧЦ0 – соответственно блок 16-битных

регистров текущего числа циклов и регистров базового числа циклов, загружаемых

системным процессором начальным значением. Во время ПДП содержимое РТЧЦ3-РТЧЦ0

меняется после завершения каждого цикла путем передачи данных между РТЧЦ и Сч.

Сч – двоичный 16-битный счетчик, осуществляет изменение

содержимого РТЧЦ и РТА в режиме ПДП.

РА – регистр адреса оперативной памяти, предназначен для

временного хранения текущего адреса оперативной памяти, передачи его на шину

адреса оперативной памяти и передачи его на шину адреса интерфейса ISA.

РМ – регистр микрокоманд, осуществляет фиксацию 8-битной

микрокоманды, считанной из ПМ.

Инициализация КПДП

Перед

началом работы КПДП его необходимо инициализировать путем выполнения следующих

действий:

- настройки

выбранного канала путем записи в регистр режима (РР) необходимой информации;

-

вывода адреса

страницы в соответствующий данному каналу регистр РС;

-

записи начального

адреса оперативной памяти в требуемый регистр текущего адреса (РТА) канала Ki;

-

передачи кода

числа циклов в регистр текущего числа циклов (РТЧЦ) канала Ki;

-

сброса триггера Тп/п

и разрешения ПДП путём программного сброса триггера Т3 ПДП.

Запись в регистр РР выполняется по команде OUT с адресом 0Bh,

причем в самом посылаемом байте данных биты D1 и D0 определяют номер канала

(00-К0 ,01- К1, 10- К2, 11- К3, ),

для которого устанавливается соответствующий режим. Старшая часть адреса

SA9-SA4 дешифруется внешней схемой и с учетом управляющего сигнала записи

ввода/вывода в КПДП поступает сигнал -ЗпПДП, указывающий на выбор ПДП и

операцию записи данных. Младшая часть адреса SA3-SA0 направляется в КПДП для

выбора соответствующего порта. В рассматриваемом случае SA3SA2SA1SA0=1011. Этот

код с учетом низкого активного уровня сигнала –ЗпППД поступает через регистр БФ1

на адресные входы ПЗУ (Шиф) и считывает содержимое соответствующей ячейки

памяти, в которой два бита хранят номер регистра (НР) режима, поступающий на

дешифратор ДшУС. На выходе ДшУС формируется сигнал –ЗпРР, который записывает

байт данных, поступивший через приемопередатчик ПП1 на входы блока

РР3-РР0, в соответствующий РРi, причем выбор

индекса регистра режима осуществляют биты данных D1 и D0, определяющие номер

(индекс) канала.

Запись в регистр РСi производится по команде OUT с

использованием одного из следующих адресов: 083h запись адреса страницы К0;

082h - К1; 081h - К2; 080h - К3, при этом по

линиям данных SD3-SD0 передаются соответствующие биты адреса: SD3-SA19,

SD2-SA18, SD1-SA17, SD0-SA16.

Выбор нужного РСi (одного из четырех)

осуществляется битами адреса SA1 и SA0, а момент записи данных определяется

внешним сигналом записи страницы (-ЗпСтр), при формировании которого

учитывается результат дешифрации адреса РСi и наличие интерфейсного

сигнала –IOW.

Запись в 16-битный РТАN производится командой OUT с

употреблением следующих адресов: 000h-адрес РТА0, 002h-РТА1, 004-РТА2,

006-РТА3. Так как входная шина КПДП 8-битная (SD7-SD0), то вывод 16-битного

кода начального адреса выполняется двумя командами OUT, причем первая команда

передает младший байт адреса (А7-А0), а вторая команда – старший байт (А15-А8).

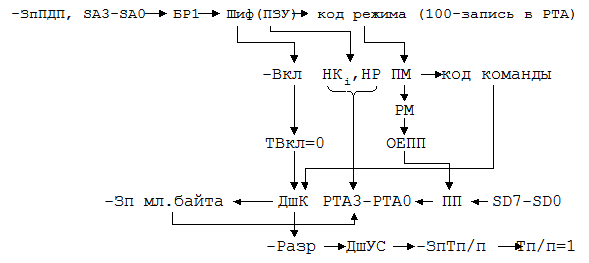

Более подробно выполнение команды OUT в этом случае

показывает следующая схема последовательности действий, представленная на рис.

2.

Рис. 2. Схема последовательности

действий КПДП при записи байта адреса в РТА

Из схемы последовательности действий видно, что входной

сигнал –ЗпПДП и младшие биты адреса SA3-SA0 через регистр БР1

поступают на адресные входы шифратора (Шиф), выполненного на базе ПЗУ. На

входах Шиф формируется 3-битный код режима (100- запись в РТА) и сигнал включения

(-Вкл), которые соответственно поступают на входы ПМ (ПЗУ) и триггер ТВкл.

Триггер ТВкл сбрасывается в нулевое состояние и разрешает работу дешифратора

ДшК, на входы которого поступает 3-битный код команды. К этому моменту времени

сигналом ОЕПП1 открыт приемопередатчик ПП1 и байт адреса

с шины SD7-SD0 поступает по внутренней шине BD7-BD0 на входы блока РТА3-РТА0 и

записывается в требуемом РТАi (младшую часть битов, А7-А0) сигналом

–Зп мл.байта. Кроме того, выполняется установка в единичное состояние триггера

Тп/п для приема следующего байта адреса в старшую часть битов РТАi

(А15-А8).

Аналогичным образом осуществляется запись в регистр текущего

числа циклов РТЧЦ путем выполнения двух команд OUT для записи вначале младшего

байта, а потом старшего байта. При этом применяются следующие адреса: 001h -

для записи в РТЧЦ канала 0, 003h – в РТЧЦ канала 1, 005h – в РТЧЦ канала 2 и

007h – в РТЧЦ канала 3.

Триггер ТЗПДП устанавливается в режим запрета ПДП по сигналу

RESET. Разрешение ПДП осуществляется командой OUT с адресом 008h, причем бит

SD2 должен быть равен 0.

Сброс триггера Тп/п выполняется без передачи бита

данных командой OUT с адресом 00Сh. Доступ к регистрам контроллера, выполняемые

операции и коды режима представлены в табл. 1.

Таблица 1

|

Адрес(h)

|

SA3

|

SA2

|

SA1

|

SA0

|

-ЧтDMA

|

-ЗпDMA

|

Операция

|

|

0C

|

1

|

1

|

0

|

0

|

1

|

0

|

Сброс Тп/п

|

|

0B

|

1

|

0

|

1

|

1

|

1

|

0

|

Запись в РР

|

|

08

|

1

|

0

|

0

|

0

|

0

|

1

|

Чтение в РС

|

|

07

|

0

|

1

|

1

|

1

|

0

|

1

|

Чтение РТЧЦ К3

|

|

05

|

0

|

1

|

0

|

1

|

0

|

1

|

Чтение РТЧЦ К2

|

|

03

|

0

|

0

|

1

|

1

|

0

|

1

|

Чтение РТЧЦ К1

|

|

01

|

0

|

0

|

0

|

1

|

0

|

1

|

Чтение РТЧЦ К0

|

|

07

|

0

|

1

|

1

|

1

|

1

|

0

|

Запись РТЧЦ К3

|

|

05

|

0

|

1

|

0

|

1

|

1

|

0

|

Запись РТЧЦ К2

|

|

03

|

0

|

0

|

1

|

1

|

1

|

0

|

Запись РТЧЦ К1

|

|

01

|

0

|

0

|

0

|

1

|

1

|

0

|

Запись РТЧЦ К0

|

|

0B

|

0

|

1

|

1

|

0

|

0

|

1

|

Чтение РТА К3

|

|

04

|

0

|

1

|

0

|

0

|

0

|

1

|

Чтение РТА К2

|

|

02

|

0

|

0

|

1

|

0

|

0

|

1

|

Чтение РТА К1

|

|

00

|

0

|

0

|

0

|

0

|

0

|

1

|

Чтение РТА К0

|

|

OB

|

0

|

1

|

1

|

0

|

1

|

0

|

Запись РТА К3

|

|

04

|

0

|

1

|

0

|

0

|

1

|

0

|

Запись РТА К2

|

|

02

|

0

|

0

|

1

|

0

|

1

|

0

|

Запись РТА К1

|

|

00

|

0

|

0

|

0

|

0

|

1

|

0

|

Запись РТА К0

|

Циклы ПДП

Рассмотрим цикл ПДП

в режиме чтения (чтение ВУ и запись в память). После того, как выполнена

инициализация КПДП и программно сброшен триггер ТЗ ПДП, указывающий на разрешение

ПДП, сигналы запроса ПДП DRQ3 – DRQ0 (один или несколько) воспринимаются Шиф,

причем наивысшим приоритетом обладает сигнал DRQ0, а низшим приоритетом сигнал

DRQ3. Таким образом, в циклах ПДП Шиф реализует функцию фиксированного

приоритета, когда предпочтение отдается сигналу запроса ПДП с меньшим номером.

С появлением одного или нескольких сигналов DRQ на входе Шиф формируется сигнал

– Вкл, который сбрасывает триггер ТВкл в нулевое состояние, тем самым

блокируется прием запросов DRQ в БР1 до конца выполнения режима,

сбрасывается счетчик микрокоманд (СчМ) и разрешается работа дешифратора ДшК.

Кроме того, Шиф выдает 2-битный код текущего номера канала (НКi),

поступающий в блок РР3-РР0, блок РС3-РС0,

блок РТА3-РТА0, блок РТЧЦ3-РТЧЦ 0 и

формирователь ФDACK. Помимо этого Шиф формирует 3-битный код режима (000 – цикл

ПДП), который подается на соответствующие адресные входы памяти микрокоманд

(ПМ). В свою очередь, ПМ через регистр РМ выдает сигнал запроса шины (HRQ).

После этого с помощью счетчика СчМ, который последовательно считывает

содержимое ПМ (ПЗУ), дешифратор ДшК последовательно формирует сигналы – Чт

младшего байта и – Чт старшего байта, по которым начальный адрес памяти из РТА

через счетчик Сч записывается в регистр РА.

Затем системный

процессор подтверждает захват шины сигналом –HLDA, который запоминается в

регистре БР2 по синхросигналу SCLK и подается на вход ПМ,

генерирующей через регистр РМ сигнал –AEN.

Сигнал –AEN и –HLDA

участвуют в формировании сигнала разрешение выходных сигналов (-РВ),

позволяющего установить биты адреса страницы (А19 – А15) из РСi и

биты адреса А15-А0 из регистра РА на шину адреса, сформировать сигнал - DACKi

на выходе ФDACK вслед за установленным адресом.

По сигналу –AEN

формирователь ФУС с учетом информации в выбранном регистре РР выдает сигнал

–IOR (чтение ввода – вывода) и затем сигнал записи в память –MEMW.

Цикл ПДП

завершается после поступления из памяти сигнала готовности I/O CH RDY, по которому

ПМ снимает –AEN, затем сбрасывает адрес, управляющие

сигналы –IOR, -MEMW и сигнал –DACK.

После этого

содержимое счетчика (Сч) увеличивается (уменьшается) на 1 и по сигналу – Зп

слова дешифратора команд (ДшК) адрес из Сч переписывается в РТАi .

Кроме того, значение РТЧЦi заносится в Сч, где оно уменьшается на 1

и снова записывается в РТЧЦi.

Затем дешифратор

ДшК формирует сигнал «-конец», устанавливающий триггер ТВкл в единичное

состояние, и становится возможным запись входных сигналов в регистр БР1.

Описанные действия повторяются до тех пор, пока содержимое Сч не станет равным

FFFFh, при этом на выходе Сч вырабатывается сигнал окончания счета (Т/С).

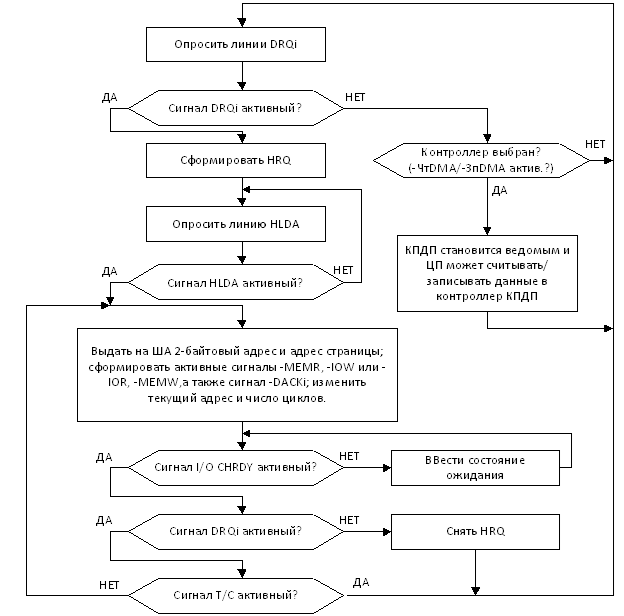

Логика действия

КПДП иллюстрируется блок-схемой, представленной на рис. 3.

Рис.

3. Блок-схема функционирования КПДП

11.3 Пример выполнения варианта задания

Разработать программу на ассемблере, выполняющую проверку

контроллера прямого доступа к памяти (кпдп)

в режимах записи (чтения) без передачи данных. После окончания заданного числа

циклов ПДП необходимо вывести на экран дисплея содержимое регистра состояния,

регистра текущего адреса, регистра текущего числа циклов.

Исходные данные:

Канал – 1.

Количество передаваемых данных – 128.

Блочный режим передачи.

.MODEL small

.STACK

100h

.DATA

CR

DB 13,10,0

Message DB

"Программа тестирования КПДП",13,10,\

"Канал1 DMA, передача 128

байтов данных.",\

"Режим блочной передачи (в

состоянии контроля).",13,10,\

"Для продолжения нажмите любую клавишу...",0

MessOk

DB 13,10,"Проверка выполнена.", 0

MessStateReg DB

13,10," Регистр состояния:",0

MessDataReg DB

13,10," Регистр данных:",0

MessCycleReg DB

13,10," Регистр текущего числа циклов:",0

TableS DB

"0123456789ABCDEF"

.CODE

mov

ax,@data

mov ds,ax

mov

si,Offset Message

Call WriteStr

mov ah,0 ;Чтение

символа с клавиатуры

int 16h

out 0dh,al

;Программный сброс контроллера

mov si,Offset MessStateReg

Call

WriteStr

in al,08h ;Чтение регистра

состояния

Call WriteChar

out 0ch,al

;Сброс триггера первый/последний

mov al,0h ;

out 02h,al ;Устанавливаем

адрес

mov al,0h ;

out

02h,al ;

mov

al,81h ;Направляем код: Блочная передача+ ;контроль

канала1 в регистр режима

out 0bh,al

;

out 0ch,al ;Сброс

триггера первый/последний

mov al,7Fh ;Помешаем

код числа циклов в порт 03h

out 3h,al ;

mov

al,0h ;

out 3h,al ;

mov al,0h ;Запись командного

слова в регистр

out

08h,al ;управления

;

mov al,05h ;Устанавливаем

программный запрос

out 09h,al ;канала1

in al,03 ;Чтение

текущего числа циклов

mov cl,al ;

in

al,03 ;

mov

ch,al ;

in al,0dh

mov dh,al ;Регистр

данных

in al,08h

mov dl,al ;Чтение регистра состояния

mov al,01h ;Снятие

запроса ПДП канала1

out 09h,al

mov

si,Offset MessOk

Call

WriteStr

mov

si,Offset MessStateReg

Call

WriteStr

mov al,dl

Call

WriteChar

mov

si,Offset MessdataReg

Call

WriteStr

mov al,dh

Call

WriteChar

mov

si,Offset MessCycleReg

Call

WriteStr

mov al,cl

Call

WriteChar

mov ah,4ch

int 21h

WRITECHAR PROC

;AL = char ;Начало процедуры вывода символа

xor ah,ah

push ax

shr al,4

mov bx,ax

mov

al,TableS[bx]

mov ah,0eh

mov bh,0

int 10h

pop ax

and

al,00001111b

mov bx,ax

mov

al,TableS[bx]

mov ah,0eh

mov bh,0

int 10h

mov ax,0E20h

xor bx,bx

int 10h

ret

WRITECHAR ENDP

WriteStr PROC ;

si -addr str ;Начало процедуры вывода строки

mov ah,0Eh;

UP:

LODSB

CMP AL,0

JZ DOWN

INT 10h

JMP UP

DOWN:

ret

WriteStr ENDP

END

11.4 Варианты заданий

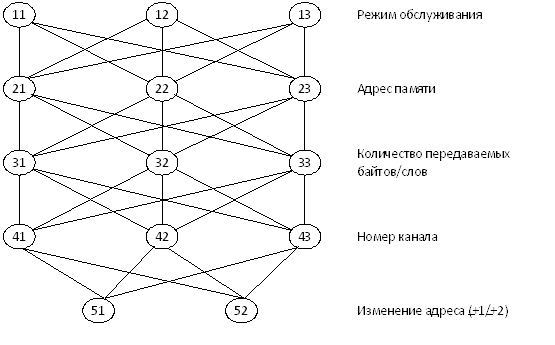

Варианты заданий представлены морфологическим графом (см.

рис. 1)

Рис. 1.

Морфологический граф вариантов заданий.

Вариант задания определяется маршрутом в графе, например,

12-21-32-41-51. Первый уровень (вершины 11, 12, 13) графа задаёт режим

обслуживания КПДП: блочный (11), одиночный (12), по требованию (13). Второй

уровень графа (вершины 21, 22, 23) соответствует выбранному адресу памяти из

адресного пространства пользователя. Третий уровень (вершины 31, 32, 33)

определяет количество передаваемых байтов/слов, например, вершине 31

соответствует 64 единицы информации, вершине 32 – 128, вершине 33 – 256.

Четвёртый уровень графа (вершины 41, 42, 43) обуславливает выбор номера канала

(К1, К3, К7), а пятый уровень (вершины 51, 52) – изменение адреса (инкремент

или декремент).

Похожие материалы:

Режим особых условий в исправительных

учреждениях

Режим исполнения наказания в виде лишения свободы (Батычко В.Т., 2007)

Режим иностранных инвестиций

Режим рабочего времени

Режим рабочего времени (Батычко В.Т., 2007)

Режим рабочего времени лиц, работающих в

религиозных организациях

|