|

В.А. Авдеев, В.Ф. Гузик

Компьютеры: шины, контроллеры, периферийные устройства

Учебное пособие. Таганрог: ТРТУ, 2001. - 536 с.

Практические задания 1,2

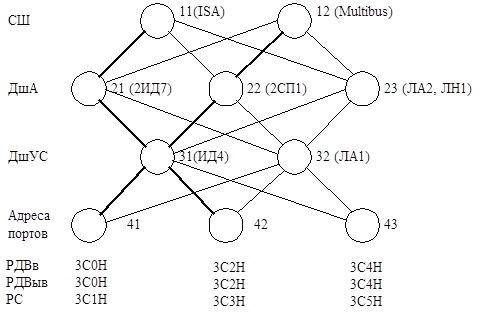

На рис. 1 представлен морфологический граф (МГ) вариантов

построения адаптера, содержащего адресуемые 8-разрядный регистр данных вывода

(РДВыв), 8-разрядный регистр данных ввода (РДВв) и 2-разрядный регистр

состояния (РС). МГ содержит четыре уровня.

Рис.

1. Морфологический граф вариантов построения адаптера.

Первый уровень – системная шина (СШ) состоит из двух вершин

11 и 12. Вершина 11 соответствует шине ISA, а вершина 12 – шине Multibus.

Второй уровень определяет тип микросхем, используемых для реализации

дешифратора адреса (ДшА). Так, ДшА можно построить на двух микросхемах 1533ИД7

(вершина 21), на двух микросхемах 1533СП1 (вершина 22) и на микросхемах 1533ЛА2

и ЛН1 (вершина 23). Третий уровень задает тип микросхем, применяемых для

построения дешифратора управляющих сигналов (ДшУС). Вершина 31

соответствует микросхеме 1533ИД4, а вершина 32 – 1533ЛА1. Последний четвертый

уровень определяет адреса портов, взятые из резерва. Этот уровень для простоты

изображения графа содержит только три вершины (41, 42 и 43). МГ задает 36

вариантов построения принципиальной схемы адаптера. Каждый вариант определяется

маршрутом МГ, проходящим через вершину каждого уровня. Например, маршрут 11,

21, 31, 42 задает вариант подключения портов к СШ ISA, ДшА должен быть

реализован на двух ИД7, ДшУС – на ИД4, адрес РДВв –3С0Н, адрес РДВыв – 3С0Н и

адрес РС – 3С1Н, причем РС доступен по записи и по чтению со стороны П. ПУ

записывает байт данных в РДВв и устанавливает бит готовности в РС, а П – бит

разрешения прерывания (РП). Кроме того, сигнал РП может быть считан П.

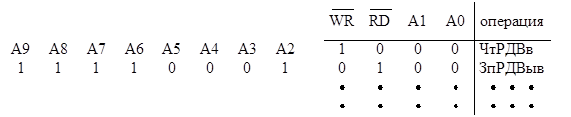

С целью быстрой проверки схемы необходимо выполнить

следующие условия: избегать шинных соединений; показать обозначения сигналов на

выходах ДшУС и ДшА, например, ЧтРДВв, ЗпРДВыв, ВыбПУ и т.д.; рядом с ДшА и ДшУС

представить соответственно двоичный эквивалент адреса и таблицу операций (рис.

2).

Рис.

2. Двоичный эквивалент адреса 3С4Н и таблица операций ДшУС.

В качестве РДВв и РДВыв предлагается использовать микросхемы

1533 ИР22, а для реализации РС – триггеры 1533 ТМ2.

Похожие материалы:

Компьютеры: шины, контроллеры, периферийные устройства. Ответы на контрольные вопросы

Компьютеры: шины, контроллеры, периферийные устройства. Контрольные вопросы 5 - Авдеев В.А. и др., 2001

Компьютеры: шины, контроллеры, периферийные устройства. Контрольные вопросы 4

Компьютеры: шины, контроллеры, периферийные устройства. Практические задания 3,4

Компьютеры: шины, контроллеры, периферийные устройства. Практические задания 5,6 - Авдеев В.А. и др., 2001

Компьютеры: шины, контроллеры, периферийные устройства. Практические задания 7,8

|