|

В.А. Авдеев, В.Ф. Гузик

Компьютеры: шины, контроллеры, периферийные устройства

Учебное пособие. Таганрог: ТРТУ, 2001. - 536 с.

6. Периферийные интерфейсы

6.10. Программируемый периферийный интерфейс

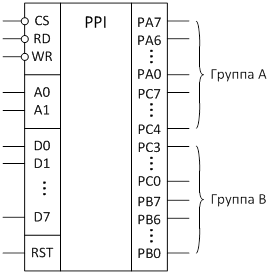

Общий вид микросхемы (PPI) I8255

(58BB55) представлен на рис. 6.21.

Рис. 6.21. Общий вид микросхемы PPI

Микросхема PPI

содержит три 8-битных порта PA, PB и PC, доступных по записи и чтению (R) со стороны процессора. Кроме того, в состав оборудования PPI входит адресуемый регистр управления

(РУ), в который микропроцессор только записывает информацию, задающую режим

работы портов и направление передачи данных.

В табл. 6.7 показаны порты PPI и сигналы, необходимые для выбора этих портов.

Таблица 6.7

|

|

|

|

A1

|

A0

|

Порт

|

Доступ

|

|

0

|

1

|

0

|

0

|

0

|

РА

|

W

|

|

0

|

1

|

0

|

0

|

1

|

РВ

|

W

|

|

0

|

1

|

0

|

1

|

0

|

РС

|

W

|

|

0

|

1

|

0

|

1

|

1

|

РУ

|

W

|

|

0

|

0

|

1

|

0

|

0

|

РА

|

R

|

|

0

|

0

|

1

|

0

|

1

|

РВ

|

R

|

|

0

|

0

|

1

|

1

|

0

|

РС

|

R

|

|

0

|

1

|

1

|

*

|

*

|

Z

|

|

1

|

*

|

*

|

*

|

*

|

Z

|

|

0

|

0

|

1

|

1

|

1

|

Запрещенная комбинация

|

Z – состояние выключено, * - безразличное состояние

PPI выполняет три режима:

-

режим 0

(ввод/вывод общего типа);

-

режим 1

(стробируемый ввод/вывод);

-

режим 2

(двунаправленная передача).

В

режиме 0 используются два 8-битных порта РА, РВ и два 4-битных порта РС (3-0),

РС (7-4), которые можно запрограммировать на ввод или вывод данных. В этом

режиме можно задать 16 конфигураций: РАРВРС(3-0)РС(7-4), РА¯РВ РС(3-0)РС(7-4), …, РА¯РВ¯РС(3-0)¯РС(7-4), где знаками и ¯

соответственно отмечены ввод и вывод данных.

Если в режиме 0 используется безусловный способ обмена, то в

режиме 1- обмен в режиме опроса флага готовности или прерывания с

использованием портов РА и РВ, а некоторые биты порта РС, входящие в состав

группы, употребляются для формирования сигналов квитирования и прерывания.

В режиме 2 применяется только порт А для образования канала с

двунаправленной передачей данных с квитированием и прерыванием.

Регистр РУ используется для хранения управляющего слова

режима работы (его бит D7=1)

или для хранения управляющего слова установки/сброса битов порта РС (его бит D7=0).

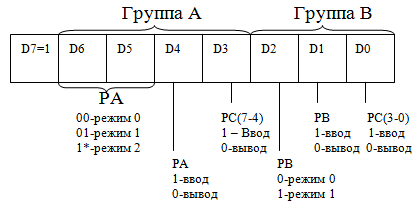

Формат управляющего слова режима работы представлен на рис.

6.22.

Рис.

6.22. Формат управляющего режима работы

Порты РА и РС(7-4) образуют группу А, а порты РВ и РС(3-0) –

группу B. В битах D6 и D5

формата управляющего слова задается режим работы порта РА, а в бите D4

указывается направление передачи данных (1- данные вводятся в процессор, 0 –

данные выводятся из процессора). Аналогичным образом объясняется назначение

битов группы B.

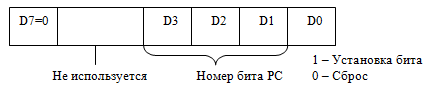

На рис. 6.23 изображен формат управляющего слова

установки/сброса битов порта РС.

Рис. 6.23. Формат управляющего слова установки/сброса битов

РС

С помощью этого управляющего слова можно установить или

сбросить любой бит порта РС. Управляющее слово установки/сброса бита

используется для разрешения прерывания, т.е. для установки соответствующих

битов порта РС, предназначенных для этой цели.

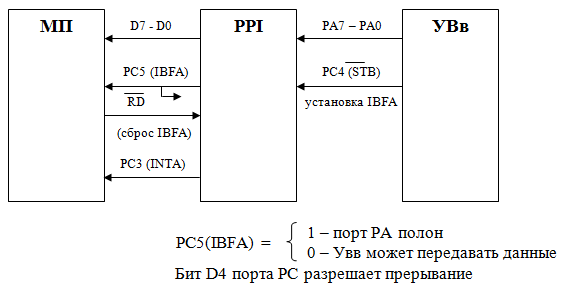

Рассмотрим режим 1 PPI (ввод данных

из порта РА). На рис. 6.24 показана схема соединения устройства ввода (Увв), PPI и МП в этом режиме.

Рис. 6.24. Схема

ввода данных из РА в режиме 1

В режиме 1 для порта А и при условии ввода данных Увв

направляет байт данных по линиям РА7-РА0 и затем записывает его сигналом строб

( ), установленным на линии РС4. По сигналу ), установленным на линии РС4. По сигналу

, кроме того, формируется сигнал IBFA на линии РС5, который указывает МП,

что порт РА полон. При чтении данных из порта А микропроцессором выполняется

автоматический сброс сигнала IBFA.

Для разрешения прерывания используется бит D4 порта РС. Если бит D4 порта РС равен 1 и установлен сигнал IBFA, то на линии РС3 формируется сигнал

прерывания INTA, сообщающий МП, что порт РА полон.

Сигнал IBFA, равный 0, указывает УВв, что оно

может передавать данные в порт РА. Так достигается координация действий МП, PPI и Увв. Неиспользуемые биты D5 и D4 порта РС группы А могут быть запрограммированы для ввода

или вывода битов данных. , кроме того, формируется сигнал IBFA на линии РС5, который указывает МП,

что порт РА полон. При чтении данных из порта А микропроцессором выполняется

автоматический сброс сигнала IBFA.

Для разрешения прерывания используется бит D4 порта РС. Если бит D4 порта РС равен 1 и установлен сигнал IBFA, то на линии РС3 формируется сигнал

прерывания INTA, сообщающий МП, что порт РА полон.

Сигнал IBFA, равный 0, указывает УВв, что оно

может передавать данные в порт РА. Так достигается координация действий МП, PPI и Увв. Неиспользуемые биты D5 и D4 порта РС группы А могут быть запрограммированы для ввода

или вывода битов данных.

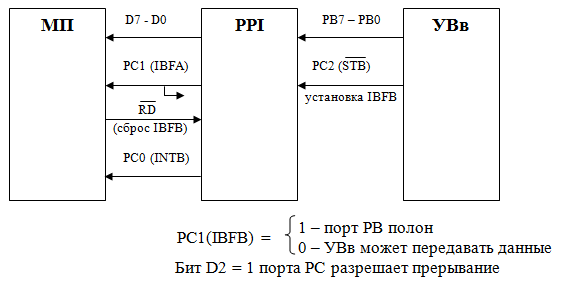

Аналогичным образом выполняется ввод данных из порта РВ в

режиме 1. На рис. 6.25 представлена схема ввода данных из РВ в режиме 1.

Рис.

6.25. Схема ввода данных из РВ в режиме 1

Неиспользуемые биты D4 и D5 порта РС в этом режиме могут быть

употреблены для ввода или вывода битов данных.

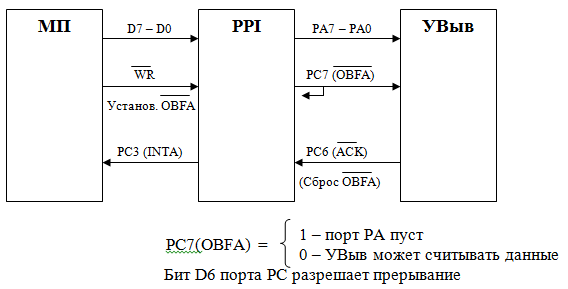

Схема вывода данных из МП в порт РА в режиме 1 изображена на

рис. 6.26.

Рис.

6.26. Схема вывода данных из МП в порт РА в режиме 1

В этом режиме МП выводит данные с указанием адреса порта РА.

Запись данных в порт РА выполняется сигналом  ,

по которому, кроме того, формируется на линии РС7 сигнал ,

по которому, кроме того, формируется на линии РС7 сигнал  , сообщающий устройству вывода (Увыв) о

наличии данных на линиях РА7 – РА0. Увыв принимает данные и устанавливает

ответный квитирующий сигнал , сообщающий устройству вывода (Увыв) о

наличии данных на линиях РА7 – РА0. Увыв принимает данные и устанавливает

ответный квитирующий сигнал  (подтверждение),

сбрасывающий сигнал (подтверждение),

сбрасывающий сигнал  . Высокий уровень

сигнала OBFA указывает МП, что порт РА пуст и можно

выводить очередной байт данных. Формирование сигнала прерывания на линии РС3 (INTA) возможно, если установлены бит D6

порта РС, разрешающий прерывание, и сигнал OBFA = 1

(порт РА пуст). Биты D4 и D5

порта РС, относящиеся к группе А, могут быть запрограммированы на ввод или

вывод. . Высокий уровень

сигнала OBFA указывает МП, что порт РА пуст и можно

выводить очередной байт данных. Формирование сигнала прерывания на линии РС3 (INTA) возможно, если установлены бит D6

порта РС, разрешающий прерывание, и сигнал OBFA = 1

(порт РА пуст). Биты D4 и D5

порта РС, относящиеся к группе А, могут быть запрограммированы на ввод или

вывод.

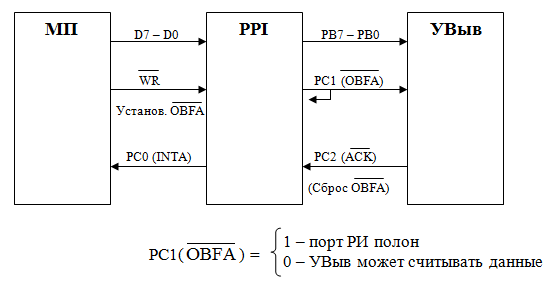

Аналогичная схема по принципу действия представлена

для порта РВ (рис. 6.27).

Рис. 6.27. Схема вывода данных из МП в порт РВ в режиме 1

В режиме 2 используется порт А, выполняющий ввод и вывод данных,

т.е. доступный по записи и чтению со стороны МП (рис. 6.28), благодаря чему

образуется двусторонняя шина данных.

Рис.

6.28. Схема ввода/вывода данных в режиме 2

Если порт РА использует режим 2, то порт РВ может работать в

режиме 0 или режиме 1.

Похожие материалы:

Программирование контроллера НЖМД

Программирование контроллера НГМД - Авдеев В.А. и др., 2001

Программа предоставления

государственных финансовых и государственных экспортных кредитов

Программный обмен

Программы для ЭВМ - ст.1261 ГК РФ

Программы для ЭВМ

|