|

В.А. Авдеев, В.Ф. Гузик

Компьютеры: шины, контроллеры, периферийные устройства

Учебное пособие. Таганрог: ТРТУ, 2001. - 536 с.

10. Устройства ввода и регистрации информации

10.8. Стандарт IEEE1284

Стандарт IEEE1284 параллельного интерфейса определяет пять режимов

обмена данными для параллельного порта (ППТ):

1.

Режим Centronics.

2.

Режим Centronics с полубайтным вводом данных.

3.

Режим Centronics с байтовым вводом данных.

4.

Режим EPP (усовершенствованного параллельного

порта).

5.

Режим ECP (порта с расширенными функциями).

Исходный режим Centronics характеризуется байтовой

однонаправленной программированной передачей (выводом) данных с квитированием и

выводом пяти битов состояния ПУ.

Второй режим сохраняет протокол

обмена данными режима Centronics и дополнительно реализует возможность 4-битного ввода байта данных ПУ за

два цикла с использованием линий состояния ПУ.

Третий режим также использует

протокол Centronics и двунаправленную шину с возможностью

ввода байта данных в хост (процессор) со стороны ПУ.

Четвертый режим (EPP) употребляет собственный протокол

обмена в режиме ввода/вывода и содержит байтовую двунаправленную шину

адреса/данных.

Пятый режим (ECP) обеспечивает двунаправленную передачу данных с их

буферизацией, предусматривает сжатие данных, применение ПДП и программного

ввода/вывода.

Стандарт IEEE1284 устанавливает типы используемых разъемов: DB 25, 36-контактный разъем Centronics и 36-контактный малогабаритный

разъем. Общий вид разъема DB 25

изображен на рис.10.13.

Рис.10.13.

Разъем DB25P

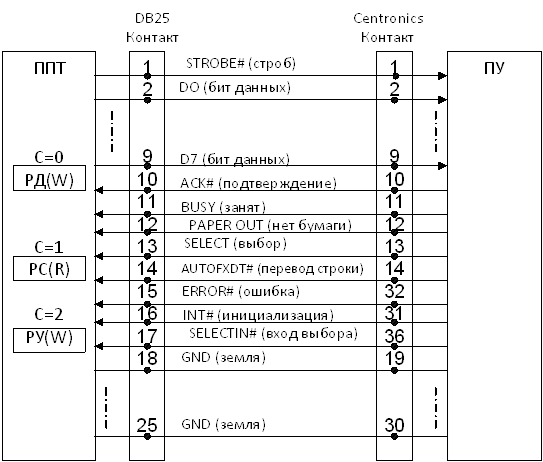

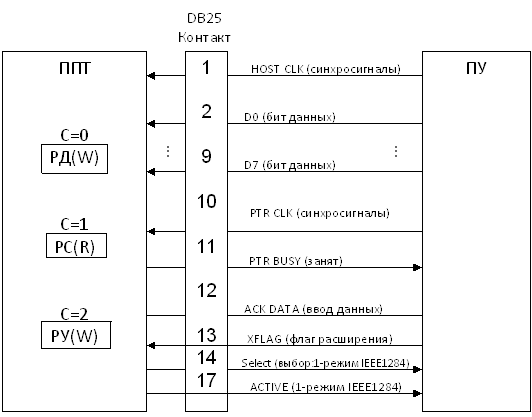

Схема связи ППТ и ПУ в режиме Centronics представлена на

рис. 10.14.

Рис.

10.14. Схема связи ППТ и ПУ в режиме Centronics

Как уже указывалось, ППТ содержит три адресуемых регистра:

регистр данных (РД(W)), доступный по

записи (W) и имеющий смещение относительно

базового адреса С=0; регистр состояния (РС(R)) со смещением С=1, доступный по чтению (R) со стороны процессора; регистр

управления (РУ(W)), которому

соответствует смещение С=2 и содержимое которого может быть записано из

процессора.

Временная диаграмма программно-управляемого режима Centronics была рассмотрена раньше.

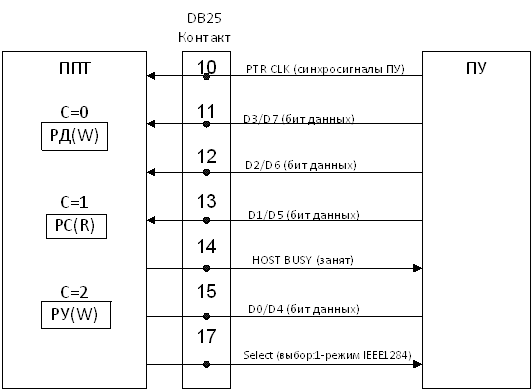

Схема соединения ППТ и ПУ для реализации второго режима только

с учетом полубайтного ввода показана на рис. 10.15.

Рис.

10.15. Схема полубайтного ввода

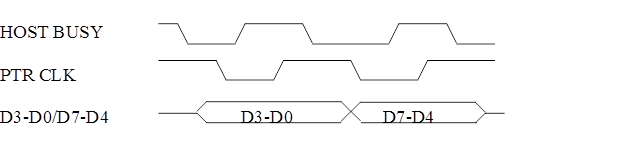

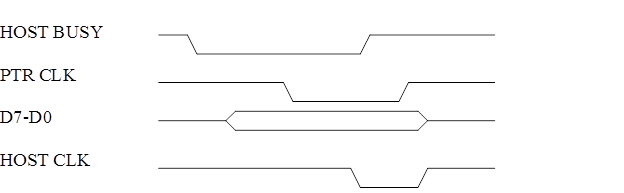

Временная

диаграмма ввода тетрад данных из ПУ в хост (процессор) представлена на рис.

10.16.

Рис.

10.16. Временная диаграмма ввода тетрад данных

Хост сигналом HOST BUSY низкого

уровня указывает на готовность приема тетрад данных со стороны ПУ. ПУ

устанавливает тетрады данных и затем сигналы PTR CLK, низкий уровень которых указывает на достоверность

данных. Из-за небольшой пропускной способности этот режим имеет ограниченную

область применения.

Третий режим (двунаправленный порт) выполняется путем

установки бита D5 регистра РУ(W) ППТ.

На рис. 10.17 изображена схема соединения ППТ и ПУ для

выполнения режима байтного ввода.

Рис.

10.17. Режим байтного слова

Временная

диаграмма ввода данных для третьего режима (байтового ввода) изображена на рис.

10.18.

Рис. 10.18. Временная

диаграмма байтового ввода

Хост устанавливает сигнал HOST BUSY, низкий уровень которого указывает ПУ на возможность

вводить данные. ПУ направляет данные по шине D7-D0 и устанавливает

затем сигнал PTRCLK, определяющий низким уровнем

достоверность байта на шине D7-D0. После этого хост устанавливает

сигнал HOST BUSY высокого уровня и подтверждает прием байта данных

сигналом HOSTCLK.

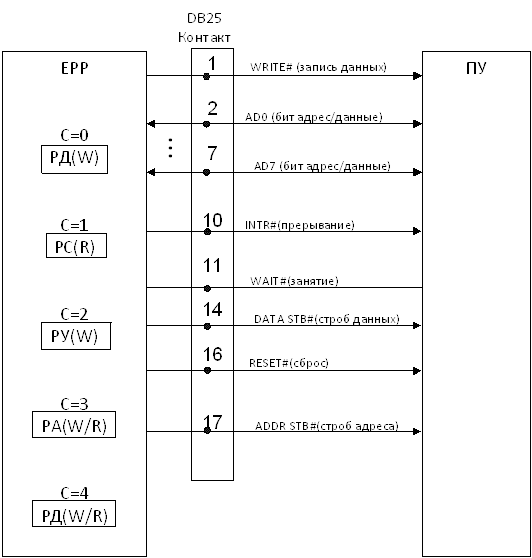

Режим EPP

выполняет следующие циклы обмена данными: записи и чтения данных, записи и

чтения адреса.

На рис. 10.19 представлена схема связи EPP с расширенным набором регистров и

ПУ.

Рис.

10.19. Схема связи EPP и ПУ

EPP дополнительно содержит: регистр адреса (РА(W/R)), чтение или запись в который генерирует соответствующий

цикл адреса EPP, и регистр данных (РД(W/R)), при записи или чтении которого выполняется

соответствующий цикл данных EPP.

Временная диаграмма цикла записи данных или адреса изображена

на рис. 10.20.

Рис.

10.20. Временная диаграмма цикла записи EPP

В приведенной диаграмме показано, что операция «запись» (IOW#) со стороны процессора инициирует внешний цикл обмена с EPP и ПУ. В этом цикле EPP устанавливает

данные или адрес и сигнал WRITE# низкого уровня. Если

на соответствующем входе EPP присутствует низкий

уровень сигнала WAIT, то EPP

формирует сигнал строба DATA STB# или ADDR STB#, выполняющий запись

установленных данных в ПУ.

Снятие строба происходит после принятия сигнала WAIT высокого уровня.

Аналогичным образом выполняется цикл чтения данных или

адреса, которые инициализируются при чтении РД(W/R) или РА(W/R).

Например, при чтении данных EPP устанавливает сигнал DATA STB#, на

которые ПУ отвечает посылкой данных, сопровождаемых сигналом WAIT#.

Снятие строба DATA STB# вызывает сброс сигнала WAIT и

данных. Длительность обмена регулируется с помощью сигнала WAIT.

Достоинством EPP является достаточно

высокая скорость обмена данными до 2 Мбайт/с с сохранением режима Centronics. Регистровая передача без буферизации данных в EPP позволяет использовать этот порт для работы в реальном

масштабе времени в устройствах связи с объектами, сбора и распределения

информации. Следует отметить, что в микросхеме I8255

(программируемом параллельном интерфейсе) реализованы более широкие

возможности, чем в EPP. Известны другие параллельные

периферийные интерфейсы со встроенными циклами обмена, например, представленный

здесь контроллер ISA/ИРПР.

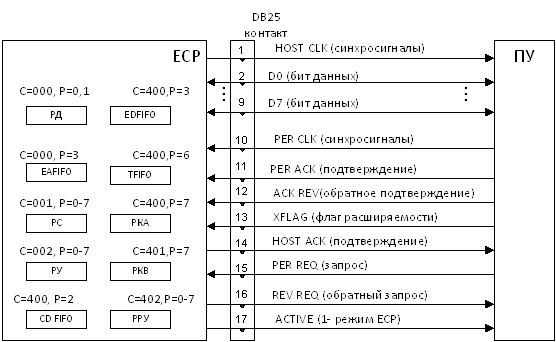

Режим ЕСР обеспечивает двунаправленный и аппаратный протокол

обмена данными хоста и ПУ, в котором выполняются циклы записи и чтения данных

или команд.

Командные циклы связаны с передачей адресов логических

устройств, входящих в состав физической системы, или содержимого счетчика RLE (группового кодирования), используемого при сжатии

данных. ЕСР выполняет следующие функции: сжатие данных методом группового

кодирования, применение FIFO для прямого и обратного

каналов, использования ПДП и программного ввода/вывода, поддержка режима Centronics. Схема связи ЕСР и ПУ показана на рис. 10.21.

Рис.

10.21. Схема связи ЕСР и ПУ

ЕСР сохраняет преемственность с параллельным портом

интерфейса Centronics. Для выполнения этой цели в ЕСР

сохранены регистры РД, РС и РУ, имеющие смещения С, соответственно равные 0, 1

и 2. Режимы (Р) работы ЕСР задаются битами D7-D5 расширенного

регистра управления (РРУ), используемого во всех режимах (Р=0-7) и имеющего

С=402h (величина смещения определена в

16–ричной форме). Режимы ECP

представлены в табл. 10.2.

Таблица 10.2

|

Режимы

|

Назначение режима

|

|

0

|

Centronics

|

|

1

|

Двунаправленный режим

|

|

2

|

Быстрый Centronics (FIFO и ПДП)

|

|

3

|

Режим параллельного порта

ЕСР

|

|

4

|

Режим параллельного порта

ЕРР

|

|

5

|

Резерв

|

|

6

|

Режим тестирования

|

|

7

|

Режим конфигурации

|

Режим Р0 является обычным режимом Centronics, а режим Р1 – режимом Centronics с обратной передачей данных, которая

определяется установкой бита D5

регистра РУ.

Режим Fast Centronics (быстрый Centronics) заключается в том, что все рутинные

программируемые операции (запись, опрос состояния и т.д.) по передаче данных в

ПУ выполняет ЕСР, а процессор осуществляет только вывод данных. Для реализации

этого режима применяется буфер FIFO и

ПДП. Запрос прерывания формируется в зависимости от состояния буфера FIFO.

Режим Р3

также использует буфер FIFO и

ПДП. С помощью регистров EDFIFO

и EAFIFO в буфер FIFO помещаются соответственно данные и команды ,

передаваемые в ПУ. Из буфера FIFO

данные выводятся через регистр EDFIFO

с учетом состояния линий HOSTACK.

Режим ЕСР предусматривает сжатие данных методом группового кодирования (RLE). Принцип кодирования состоит в том,

что учитываются одинаковые байты и отмечается в счетчике число их повторов.

Если передаются одинаковые байты, то в регистр EAFIFO заносится байт, содержащий нулевой бит D7 и счетчик числа повторов (биты D6 – D0), а в регистр EDFIFO – байт данных. Эти два байта затем используются при расширении данных в

ПУ, при приеме данных аппаратным способом и размещение их в буфере FIFO.

Режим Р6

является режимом тестирования (псевдопередача), когда данные не передаются на

внешнюю шину и проверяется работа буфера FIFO с помощью регистра TFIFO, в который данные поступают в режиме ПДП или

программного обмена. ЕСР следит за состоянием буфера FIFO и при необходимости формирует запрос прерывания.

Режим Р7

используется для получения доступа к регистрам конфигурации.

Для

обращения к регистрам ЕСР употребляются 10 двоичных битов и каждый режим

задается соответствующей записью в расширенный регистр управления (РРУ), причем

по умолчанию устанавливается режим Р0 или Р1.

Регистр EAFIFO предназначен для хранения байта

канального адреса или счетчика RLE

(назначение этого байта определяется битом D7), передаваемого в буфер FIFO в режиме ЕСР.

В регистр CDFIFO данные передаются в программном

режиме или ПДП и через буфер FIFO

направляются в ПУ в соответствии с протоколом Centronics.

Регистр TFIFO используется в режиме тестирования,

а регистр EDFIFO – в режиме ЕСР (Р3).

Код

идентификации адаптера размещается в битах D7 – D4

регистра конфигурации А (РКА), идентификация которого может быть считана хостом

, а в регистре конфигурации В (РКВ) хранится информация, необходимая драйверу.

Расширенный регистр управления (РРУ) применяется во всех

режимах и его установленные биты имеют следующее назначение: D0 – буфер FIFO пуст, D1 –

буфер FIFO полон, D2 – запрет сервисных прерываний (переполнения, опустошения,

окончания циклов ПДП), D3 –

разрешение ПДП, D4 – запрет

прерывания при наличии ошибки, D5 – D7 – режим ЕСР. Работа с портом ЕСР

заключается в программном доступе к соответствующим регистрам и слежении за

состоянием буфера FIFO.

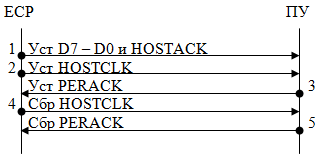

Последовательность передачи информации из ЕСР в ПУ изображена

на рис. 10.22.

Рис.

10.22. Последовательность передачи информации из ЕСP в

ПУ

Передача данных или команд имеет одну и ту же

последовательность сигналов и определяется уровнем сигнала HOSTACK

(высокий уровень – передача данных и низкий уровень – передача команды). При

выводе данных ЕСР устанавливает (уст) D7 – D0 и сигнал HOSTACK. Затем ЕСР

формирует сигналы HOSTCLK низкий уровень которых

определяет достоверность данных D7 – D0.

ПУ отвечает сигналом подтверждения периферии (PERACK)

высокого уровня. Сброс (сбр) сигнала HOSTCLK

(положительный фронт) может быть использован для записи данных и этот момент

времени определяет выдачу данных в ПУ. Если выполняется передача команды, то

это, как уже отмечалось, может быть адрес (бит D7=1)

или счетчик RLE (бит D7=0).

Драйвер выполняет вывод данных в буфер FIFO

в программном режиме или в режиме ПДП, а передача данных из буфера FIFO в ПУ осуществляется схемным способом.

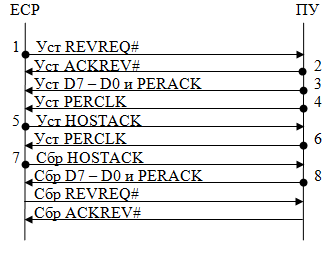

Последовательность сигналов передачи информации из ПУ в ЕСР

представлена на рис. 10.23.

Рис. 10.23. Последовательность сигналов передачи информации

из ПУ в ЕСР

При выполнении последовательности передачи информации из ПУ

в ЕСР осуществляются следующие действия:

1.

Хост

устанавливает сигнал запроса реверса передачи данных (REVREQ#) низким активным уровнем.

2.

ПУ отвечает

сигналом подтверждения реверса (ACKREV#).

3.

После этого ПУ

помещает данные D7 – D0 и устанавливает сигнал PERACK. Если PERACK имеет высокий уровень, то передаются данные, а если

низкий уровень, то направляется команда.

4.

Затем ПУ

формирует периферийный синхросигнал (РЕРСLK), низкий уровень которого указывает на достоверность

информации на D7 – D0.

5.

Хост, в свою

очередь, устанавливает сигнал HOSTACK

высокого уровня.

6.

Для фиксации

информации в ЕСР ПУ формирует сигнал PERCLK.

7.

Хост переводит

уровень сигнала HOSTACK с высокого

на низкий.

8.

ПУ, получив

сигнал HOSTACK = 0, снимает информацию с линий D7 – D0 и сбрасывает сигнал PERACK.

Указанная последовательность сигналов повторяется при вводе

каждого байта информации в ЕСР и завершается сбросом сигналов REVREQ# и ACKREV#.

При подключении какого-либо ПУ к ЕСР выполняется

последовательность установки, с помощью которой определяется тип режима ЕСР.

Если ПУ не отвечает на последовательность установки, то используется исходный

режим Centronics. Когда осуществляется

последовательность установки, то хост направляет байт расширения в ПУ, а ПУ

отвечает подтверждением или посылкой идентификатора в любом режиме обратной

передачи, кроме ЕРР. В табл. 10.3 представлено описание байтов расширения.

Таблица 10.3

|

Номер бита

|

Назначение байта расширения

|

Допустимые комбинации бит

|

|

7

|

Запрос будущих расширений

|

1000 0000

|

|

6

|

Запрос режима ЕРР

|

0100 0000

|

|

5

|

Запрос режима ЕСР с RLE

|

0110 0000

|

|

4

|

Запрос режима ЕСР без RLE

|

0010 0000

|

|

3

|

Резерв

|

0000 1000

|

|

2

|

Режим полубайтного ввода

|

0000 0100

|

|

Режим байтного ввода

|

0000 0101

|

|

Режим ЕСР с RLE

|

0011 0100

|

|

Режим ЕСР без RLE

|

0001 0100

|

|

1

|

Резерв

|

0000 0010

|

|

0

|

Запрос режима байтного ввода

|

0000 0001

|

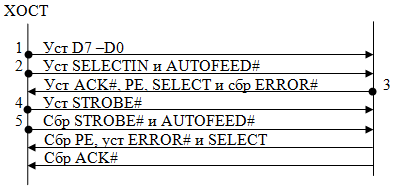

Последовательность согласования хоста и ПУ изображена на

рис. 10.24.

Рис. 10.24.

Последовательность согласования хоста и ПУ

Последовательность согласования состоит из следующих

действий:

1.

Хост

устанавливает байт расширения на линии D7 – D0.

2.

Затем хост

формирует активные уровни сигналов SELECTIN (высокий)

и AUTOFEED# (низкий), задающие начало

последовательности согласования.

3.

ПУ отвечает

сигналами: АСК# (низкий), РЕ (высокий) и ERROR# (высокий), если оно способно продолжить согласование

режима интерфейса.

4.

Хост

устанавливает активный уровень сигала STROBE# (низкий), записывающий байт расширения в ПУ.

5.

После этого хост

сбрасывает сигналы STROBE# и AUTOFEED# в пассивный высокий уровень.

6.

Если ПУ имеет

дуплексный канал, то оно формирует сигнал РЕ высокого уровня и сигнал ERROR# низкого уровня, и если запрошенный

режим подтверждается ПУ, то им устанавливается сигнал SELECT высокого уровня и в противном случае – низкого.

7.

Завершение

последовательности согласования определяется сбросом ПУ сигнала ACK# (переводом его в высокий уровень).

Для подключения к ПК большинства современных принтеров,

сканеров, Zip-накопителей используется стандарт IEEE 1284. Тип режима ППТ: EPP, ECP или Centronics задается BIOS ПК. С помощью опции AT (Centronics), PS/2 и ECP

осуществляются соответствующие изменения в CMOS Setup.

Похожие материалы:

Сталийное время

Сталеплавильное производство: Раздел ЕТКС

Сталевар электропечи

Стандартизация в системе управления качеством

Орлов А.И. Математика случая: Вероятность и статистика – основные факты: Стандартное нормальное распределение и центральная предельная теорема

Стандартные налоговые

вычеты

|